- Tổng quan

- Nội dung

- Tiêu chuẩn liên quan

- Lược đồ

- Tải về

Tiêu chuẩn Quốc gia TCVN 10895-1:2015 IEC 61193-1:2001 Hệ thống đánh giá chất lượng-Phần 1: Ghi nhận và phân tích các khiếm khuyết trên các khối lắp ráp tấm mạch in

| Số hiệu: | TCVN 10895-1:2015 | Loại văn bản: | Tiêu chuẩn Việt Nam |

| Cơ quan ban hành: | Bộ Khoa học và Công nghệ | Lĩnh vực: | Công nghiệp |

|

Ngày ban hành:

Ngày ban hành là ngày, tháng, năm văn bản được thông qua hoặc ký ban hành.

|

31/12/2015 |

Hiệu lực:

|

Đã biết

|

| Người ký: | Đang cập nhật |

Tình trạng hiệu lực:

Cho biết trạng thái hiệu lực của văn bản đang tra cứu: Chưa áp dụng, Còn hiệu lực, Hết hiệu lực, Hết hiệu lực 1 phần; Đã sửa đổi, Đính chính hay Không còn phù hợp,...

|

Đã biết

|

TÓM TẮT TIÊU CHUẨN VIỆT NAM TCVN 10895-1:2015

Tiêu chuẩn Quốc gia TCVN 10895-1:2015 về Ghi Nhận và Phân Tích Khiếm Khuyết Trên Tấm Mạch In

Ngày 31/12/2015, Bộ Khoa học và Công nghệ đã công bố "Tiêu chuẩn Quốc gia TCVN 10895-1:2015 IEC 61193-1:2001 Hệ thống đánh giá chất lượng - Phần 1: Ghi nhận và phân tích các khiếm khuyết trên các khối lắp ráp tấm mạch in". Bản tiêu chuẩn này có hiệu lực ngay từ ngày công bố.

Tiêu chuẩn này quy định các phương pháp ghi nhận và phân tích các khiếm khuyết trên các khối lắp ráp tấm mạch in, nhằm so sánh và cải thiện chất lượng sản phẩm qua các quy trình và địa điểm sản xuất khác nhau. Phạm vi áp dụng của tiêu chuẩn bao gồm việc thu thập dữ liệu khiếm khuyết qua hai loại: Loại 1 phục vụ mục đích so sánh chung, Loại 2 dành cho đánh giá quy trình cụ thể.

Các Phương Pháp Ghi Nhận Khiếm Khuyết

Tiêu chuẩn đưa ra các chỉ tiêu để phân loại các khiếm khuyết dựa trên các quy trình như áp kem hàn, áp keo dính, sắp đặt linh kiện và gắn bằng hàn. Mỗi quy trình sẽ có các tiêu chí riêng để đánh giá, từ việc đặt chệch linh kiện cho đến lượng kem hàn hay keo dính áp dụng.

Dữ Liệu Ghi Nhận Khiếm Khuyết

Khiếm khuyết cần được ghi nhận ở mức độ mối hàn, với các tiêu chí chấp nhận cụ thể. Các mẫu ghi nhận sẽ bao gồm thông tin về vị trí và loại khiếm khuyết, số lượng khiếm khuyết tại vị trí liên quan, cũng như số tấm mạch in được kiểm tra.

Xử Lý Dữ Liệu Khiếm Khuyết

Các dữ liệu thu thập được sử dụng để xác định tỷ lệ ppm (parts per million) của lô sản xuất được kiểm tra. Mức ppm được tính dựa trên số lượng khiếm khuyết và tổng số mối hàn trong lô. Tiêu chuẩn cũng khuyến nghị phương pháp phân tích như phân tích Pareto để nhận diện những kiểu khiếm khuyết phổ biến cần được khắc phục trước tiên nhằm nâng cao chất lượng sản phẩm.

Phân Tích Khiếm Khuyết

Tiêu chuẩn khuyến nghị rằng các khiếm khuyết nên được phân loại theo nguồn gốc để dễ dàng xác định nguyên nhân và cải tiến. Các quy trình phụ, vật liệu và thiết kế đều có thể là nguyên nhân dẫn đến các khiếm khuyết mà nên được điều chỉnh để tối ưu hóa quy trình sản xuất.

Bản tiêu chuẩn góp phần quan trọng trong việc thiết lập sự đồng nhất trong ghi nhận, phân tích và đánh giá chất lượng sản phẩm thiết bị điện tử, đặc biệt là trong lĩnh vực sản xuất tấm mạch in.

Tải tiêu chuẩn Việt Nam TCVN 10895-1:2015

TIÊU CHUẨN QUỐC GIA

TCVN 10895-1:2015

IEC 61193-1:2001

HỆ THỐNG ĐÁNH GIÁ CHẤT LƯỢNG - PHẦN 1: GHI NHẬN VÀ PHÂN TÍCH CÁC KHIẾM KHUYẾT TRÊN CÁC KHỐI LẮP RÁP TẤM MẠCH IN

Quality assessment systems - Part 1: Registration and analysis of defects on printed board assemblies

Lời nói đầu

TCVN 10895-1:2015 hoàn toàn tương đương với IEC 61193-1:2001;

TCVN 10895-1:2015 do Ban kỹ thuật tiêu chuẩn quốc gia TCVN/TC/E3 Thiết bị điện tử dân dụng biên soạn, Tổng cục Tiêu chuẩn Đo lường Chất lượng đề nghị, Bộ Khoa học và Công nghệ công bố.

Bộ TCVN 10895 (IEC 61193), Hệ thống đánh giá chất lượng, gồm các phần:

- TCVN 10895-1:2015 (IEC 61193-1:2001), Phần 1: Ghi nhận và phân tích các khiếm khuyết trên các khối lắp ráp tấm mạch in

- TCVN 10895-2:2015 (IEC 61193-2:2007), Phần 2: Lựa chọn và sử dụng phương án lấy mẫu để kiểm tra linh kiện điện tử và gói linh kiện điện tử

HỆ THỐNG ĐÁNH GIÁ CHẤT LƯỢNG - PHẦN 1: GHI NHẬN VÀ PHÂN TÍCH CÁC KHIẾM KHUYẾT TRÊN CÁC KHỐI LẮP RÁP TẤM MẠCH IN

Quality assessment systems - Part 1: Registration and analysis of defects on printed board assemblies

1. Phạm vi áp dụng

Tiêu chuẩn này xác định các phương pháp ghi nhận và phân tích các khiếm khuyết trên các khối lắp ráp tấm mạch in bằng cách hàn. Các phương pháp được mô tả là cho phép so sánh một cách hiệu quả tính năng giữa các sản phẩm, các quy trình và địa điểm sản xuất, và có thể lấy làm cơ sở để cải thiện chất lượng chung.

Tiêu chuẩn này quy định việc thu thập dữ liệu khiếm khuyết theo hai loại.

Dữ liệu ppm Loại 1: loại này cung cấp dữ liệu cho mục đích ghi nhận để cho phép so sánh tính năng tổng thể của các hoạt động lắp ráp.

Dữ liệu ppm Loại 2: loại này cung cấp dữ liệu dành cho việc đánh giá các quy trình con riêng lẻ, các mục đích phân tích và kiểm soát.

2. Tài liệu viện dẫn

Các tài liệu viện dẫn sau đây là cần thiết cho việc áp dụng tiêu chuẩn này. Đối với các tài liệu viện dẫn ghi năm công bố thì áp dụng phiên bản được nêu. Đối với các tài liệu viện dẫn không ghi năm công bố thì áp dụng phiên bản mới nhất (kể cả các sửa đổi).

IEC 60194, Printed board design, manufacture and assembly - Terms and definitions (Thiết kế, chế tạo và lắp ráp tấm mạch in - Thuật ngữ và định nghĩa)

IEC 61191-1, Printed board assemblies - Part 1: Generic specification - Requirements for soldered electrical and electronic assemblies using surface mount and related assembly technologies (Khối lắp ráp tấm mạch in - Phần 1: Quy định kỹ thuật chung - Yêu cầu đối với các khối lắp ráp điện và điện tử hàn bằng cách sử dụng công nghệ dán bề mặt và các công nghệ lắp ráp liên quan)

IEC 61191-2, Printed board assemblies - Part 2: Sectional specification - Requirements for surface mount soldered assemblies (Khối lắp ráp tấm mạch in - Phần 2: Quy định kỹ thuật từng phần - Yêu cầu đối với các khối lắp lắp ráp hàn dán bề mặt)

IEC 61191-3, Printed board assemblies - Part 3: Sectional specification - Requirements for through - hole mount soldered assemblies (Khối lắp ráp tấm mạch in - Phần 3: Quy định kỹ thuật từng phần - Yêu cầu đối với các lắp ráp hàn gắn qua lỗ)

IEC 61191-4, Printed board assemblies - Part 4: Sectional specification - Requirements for terminal soldered assemblies (Khối lắp ráp tấm mạch in - Phần 4: Quy định kỹ thuật từng phần - Yêu cầu đối với các khối lắp ráp hàn đầu nối)

IEC 61192-1, Product performance requirements - Part 1: Generic standard - Workmanship requirements and guidelines for soldered electronic assemblies (Yêu cầu hiệu năng sản phẩm - Phần 1: Tiêu chuẩn chung - Yêu cầu tay nghề và các hướng dẫn đối với các khối lắp ráp điện tử bằng cách hàn)

IEC 61192-2, Product performance requirements - Part 2: Sectional standard - Workmanship requirements and guidelines for soldered surface mount electronic assemblies1 (Yêu cầu tính năng sản phẩm - Phần 2: Tiêu chuẩn từng phần - Yêu cầu tay nghề và các hướng dẫn đối với các khối lắp ráp điện tử hàn bề mặt)

IEC 61192-3, Product performance requirements - Part 3: Sectional standard - Workmanship requirements for through-hole mount soldered assemblies1 (Yêu cầu tính năng sản phẩm - Phần 3: Tiêu chuẩn từng phần - Yêu cầu tay nghề đối với các khối lắp ráp điện tử hàn gắn qua lỗ)

IEC 61192-4, Product performance requirements - Part 4: Sectional standard - Workmanship requirements for terminal soldered connections1 (Yêu cầu tính năng sản phẩm - Phần 4: Tiêu chuẩn từng phần - Yêu cầu tay nghề đối với các mối nối hàn đầu cuối)

3. Thuật ngữ và định nghĩa

Tiêu chuẩn này áp dụng các định nghĩa trong IEC 60194 và các định nghĩa dưới đây. Khi thích hợp, một mã hiệu chữ - số được gán cho thuật ngữ nhằm hỗ trợ cho việc ghi nhận và loại bỏ các khiếm khuyết hoặc các chỉ thị về sai lệch với quá trình.

3.1. Đặc tính chung (general characterization)

Các điều kiện hoặc thuộc tính của khối lắp ráp điện tử cuối cùng, có thể so sánh với các yêu cầu trong tài liệu thích hợp hoặc quy định kỹ thuật về tính năng.

3.1.1. Ghi nhận khiếm khuyết (defect registration)

Hệ thống ghi nhận đồng nhất để thu thập thông tin về các thuộc tính của khối lắp ráp điện tử có thể được gán cho một quy trình con hoặc một cấu hình sản phẩm cuối cùng, được chế tạo nhưng chưa qua bất cứ bước chỉnh sửa hay sửa chữa nào.

3.1.2. Quy trình con (subprocesses)

Các chức năng chế tạo chính được sử dụng để sản xuất các khối lắp ráp điện tử là một phần tích hợp của quy trình chế tạo mà các chỉ thị về sai lệch về quy trình hoặc các khiếm khuyết quy định các thuộc tính không phù hợp có thể được quy cho quy trình chế tạo đó.

3.1.3. Mối hàn tấm mạch in (printed board solder joint)

Kết nối điện/cơ đến một tấm mạch in hoặc cấu trúc liên kết khác sử dụng chất hàn để nối hai hoặc nhiều hơn các bề mặt kim loại.

CHÚ THÍCH: Xem thêm các định nghĩa về kết nối hàn lạnh, kết nối hàn bị xáo trộn, kết nối hàn quá lượng, kết nối hàn không đủ, kết nối hàn quá nhiệt, kết nối hàn ưu tiên và kết nối hàn nhựa thông trong IEC 60194.

3.2. Áp kem hàn (P0) (solder paste application (P0))

Quy trình con được sử dụng để áp kem hàn lên khuôn cắt rãnh trên một tấm mạch in hoặc cấu trúc liên kết cho mục đích gắn các thành phần lại bằng cách sử dụng kỹ thuật hàn nóng chảy lại

3.2.1. Đặt chệch kem hàn (P1) (paste misalignment) (P1)

Hình ảnh của các biên dạng hình học của kem hàn được đặt sao cho chúng không được hiệu chỉnh vào vùng cần hàn dán trên tấm mạch in/cấu trúc liên kết được sử dụng để hàn dán các linh kiện.

3.2.2. Thừa kem hàn quá mức (P2) (excessive paste (P2))

Biên dạng hình học của kem hàn chứa lượng kem hàn lớn hơn mức xác định trong quy trình lắp ráp chi tiết.

3.2.3. Không đủ/không có kem hàn (P3) (lnsufficient/no paste (P3))

Biên dạng hình học kem hàn chứa lượng kem hàn ít hơn lượng được xác định bởi quy trình lắp ráp chi tiết.

3.2.4. Dây kem hàn (P4) (paste smearing (P4))

Việc áp kem hàn dẫn tới kết quả là kem hàn lan ra trên bề mặt hàn dán theo cách không thể kiểm soát được, thay vì có biên dạng hình học gọn gàng và được xác định rõ ràng.

3.2.5. Dính mạch do kem hàn (P5) (paste bridging (P5))

Biên dạng hình học của kem hàn tiếp xúc với hoặc nhập làm một nhiều hơn một hình mẫu dẫn.

3.2.6. Hình dạng bám tụ kem hàn (P6) (paste deposit shape (P6))

Biên dạng hình học cụ thể của kem hàn nằm trên bề mặt hàn dán của tấm mạch in như được xác định bằng cách ép kem hàn qua lỗ của khuôn in áp.

3.3. Áp keo dính (A0) (adhesive application (A0))

Quy trình con được sử dụng để áp keo dính lên bề mặt của tấm mạch in hoặc cấu trúc liên kết nhằm mục đích gắn các linh kiện theo cách để các linh kiện không xê dịch trong quy trình gắn lắp ráp.

3.3.1. Đặt chệch keo dính (A1) (adhesive misalignment (A1))

Hình ảnh các biên dạng hình học keo dính không được đặt trên lớp nền cơ sở phù hợp với vị trí được quy định trong quy trình lắp ráp chi tiết.

3.3.2. Thừa keo dính quá mức (A2) (excessive adhesive (A2))

Biên dạng hình học của keo dính chứa lượng keo dính nhiều hơn so với được xác định bởi quy trình lắp ráp chi tiết.

3.3.3. Không đủ/không có keo dính (A3) (insufficient/no adhesive (A3))

Biên dạng hình học keo dính chứa lượng keo dính ít hơn so với lượng được xác định bởi quy trình lắp ráp chi tiết, hoặc hoàn toàn không có như yêu cầu.

3.3.4. Rớt/nhiễm bẩn keo dính (A4) (adhesive stringing/contamination (A4))

Áp keo dính vào lớp nền cơ sở mà ở đó biên dạng hình học quy định trở nên không có hình dạng xác định, tạo thành các sợi mảnh kéo dài, hoặc lan sang các bề mặt mà các linh kiện phải được hàn vào.

3.3.5. Chấm hình tròn chất kết dính (A5) (adhesive dot shape (A5))

Hình dạng tròn được tạo ra, hoặc được yêu cầu, đối với các biên dạng hình học của keo dính.

3.4. Sắp đặt linh kiện (C0) (component placement (C0))

Quy trình con được sử dụng để bố trí các bộ phận điện tử và điện cơ lên trên một tấm mạch in hoặc cấu trúc liên kết, như một bước trước khi gắn linh kiện.

3.4.1. Đặt chệch linh kiện (C1) (component misalignment (C1))

Việc sắp đặt các bộ phận điện tử và điện cơ mà không khớp với các vùng cần hàn dán hoặc lỗ hổng mà theo thiết kế chúng phải được gắn vào.

3.4.2. Linh kiện bị thiếu (C2) (missing component (C2))

Các bộ phận điện tử và điện cơ không có trên tấm mạch in hoặc cấu trúc liên kết mặc dù theo yêu cầu, chúng phải có theo quy trình lắp ráp chi tiết.

3.4.3. Linh kiện lắp ngược chiều (C3) (reversed component (C3))

Các bộ phận điện tử và điện cơ đã bị định hướng sai, theo hướng ngược với quy định trong quy trình lắp ráp chi tiết.

3.4.4. Linh kiện không đúng (C4) (wrong component (C4))

Việc lựa chọn, sắp đặt hoặc gắn một bộ phận điện tử hoặc điện cơ không đúng.

3.4.5. Linh kiện trên gờ (C5) (component on edge (C5))

Bộ phận điện tử hoặc điện cơ chờm lên trên đường bao ngoài của bề mặt hàn dán.

3.4.6. Linh kiện hỏng (C6) (damaged component (C6))

Bộ phận điện tử hoặc điện cơ không phù hợp với các yêu cầu ban đầu được thiết lập bởi nhà cung cấp bộ phận do việc nâng chuyển sai hoặc phơi nhiễm bộ phận trong các điều kiện bất lợi.

3.5. Gắn bằng cách hàn (S0) (soldering attachment (S0))

Quy trình con được sử dụng để áp chất hàn, hoặc hàn nóng chảy lại kem hàn/chất hàn rắn giữa các vùng cần hàn dán trên các tấm mạch in hoặc các cấu trúc liên kết và các đầu cuối của các linh kiện điện tử hoặc điện cơ, để tạo sự gắn kết tốt về vật lý, điện và luyện kim.

3.5.1. Đặt chệch mối hàn (S1) (solder joint misalignment (S1))

(Các) biên dạng hình học của các mối hàn đã hoàn thiện không được hiệu chỉnh vào vùng cần hàn dán trên tấm mạch in/cấu trúc liên kết hoặc không trùng khớp với các bộ phận điện tử hoặc điện cơ được thiết kế để gắn lên vùng cần hàn dán hoặc một sự kết hợp của hai điều kiện này.

3.5.2. Dính mạch do mối hàn (S2) (solder joint bridging (S2))

Các biên dạng hình học của mối nối hàn đã hoàn thiện tiếp xúc với hoặc nhập làm một nhiều hơn một hình mẫu dẫn hoặc đầu cuối linh kiện

3.5.3. Không đủ/không có mối nối hàn (S3) (insufficient/no solder joint (S3))

Biên dạng hình học mối nối hàn đã hoàn thiện chứa một lượng nhỏ hơn lượng được xác định bởi quy trình lắp ráp chi tiết hoặc hoàn toàn không có như yêu cầu.

3.5.4. Dựng đứng linh kiện (S4) (component tombstoning (S4))

Bộ phận điện tử hoặc điện cơ không phù hợp với biên dạng gắn theo thiết kế do một hoặc nhiều hơn một phía có (các) đầu cuối nguội đi trước (các) đầu cuối khác khiến cho đầu của linh kiện đông đặc muộn bị nâng lên khỏi vùng cần hàn dán.

3.5.5. Linh kiện bị hỏng (S5) (damaged component (S5))

Bộ phận điện tử hoặc điện cơ không phù hợp với các yêu cầu ban đầu thiết lập bởi nhà cung cấp bộ phận, do quá trình gắn bằng cách hàn, thao tác sai khối lắp ghép, hoặc để bộ phận trong các điều kiện quy trình lắp ráp có hại.

3.5.6. Tấm mạch in hỏng (S6) (damaged printed board (S6))

Tấm mạch in/cấu trúc liên kết không phù hợp với các yêu cầu ban đầu đã thiết lập đối với sản phẩm chưa được lắp các linh kiện, do quy trình gắn bằng cách hàn, thao tác sai khối lắp ráp, hoặc để bộ phận trong các điều kiện quy trình lắp ráp có hại.

3.5.7. Thẩm thấu chất hàn (S7) (solder wicking (S7))

Di chuyển dạng mao mạch của chất hàn giữa các bề mặt kim loại, ví dụ như các sợi của dây, các lỗ mạ xuyên qua, các bề mặt cần hàn dán, hoặc các đầu cuối linh kiện điện tử/điện cơ.

3.5.8. Mối hàn nối bị xáo trộn (S8) (disturbed solder joint (S8))

Kết nối hàn đặc trưng bởi bề ngoài có sự dịch chuyển giữa các kim loại được nối khi chất hàn hóa rắn.

3.5.9. Hạt tròn nhỏ/tràn/mạng chất hàn (S9) (solder balls/splashes/webs (S9))

Mảnh chất hàn ngoại lai ở dạng những hạt tròn nhỏ, hình thù không theo quy luật, hoặc màng mỏng/lớp liên tục chất hàn, song song, nhưng không nhất thiết phải bám dính vào một bề mặt mà lẽ ra không được có chất hàn.

3.5.10. Làm ướt kém (S10) (bad wetting (S10)

Không tạo thành màng chất hàn tương đối đồng đều, mịn, liền và bám chặt vào kim loại nền, bề mặt cần hàn dán hoặc đầu cuối linh kiện điện tử/điện cơ.

4. Ghi nhận khiếm khuyết

Để ghi nhận một cách đồng nhất các khiếm khuyết, áp dụng các nguyên lý cơ bản dưới đây.

4.1. Tiêu chí chấp nhận

Tiêu chí chấp nhận/có khiếm khuyết giống như mô tả trong IEC 61191-1, IEC 61191-2, IEC 61191-3 và IEC 61191-4. Các mối nối hàn phải được đánh giá với các tiêu chí chấp nhận/có khiếm khuyết.

4.2. Đếm khiếm khuyết

Việc đếm khiếm khuyết trên sản phẩm phải được thực hiện ở mức độ mối hàn. Mối hàn không thỏa mãn các tiêu chuẩn được tính là khiếm khuyết.

CHÚ THÍCH 1: Một ngoại lệ trong phương pháp này là trường hợp dính mạch1. Dính mạch giữa hai đầu cuối (hoặc giữa một vùng cần hàn dính và một vật dẫn) chỉ được tính là một khiếm khuyết (một dính mạch), trong khi dính mạch giữa ba đầu cuối được tính thành hai khiếm khuyết (hai dính mạch), v.v.

CHÚ THÍCH 2: Trường hợp bảng mạch nhóm, đôi khi một phần của tấm mạch in không được sử dụng (các linh kiện không được đặt trong vùng cụ thể này). Không tính khiếm khuyết và tổng số mối hàn của bất kỳ phần nào của tấm mạch in không được sử dụng có chủ ý.

4.3. Ghi nhận khiếm khuyết sau hàn

Việc ghi nhận khiếm khuyết sau hàn cần được thực hiện ngay sau quy trình hàn, trước bất kì sự kiểm tra lại nào. Sản phẩm đã hàn được kiểm tra trước khi sửa chữa.

4.3.1. Khiếm khuyết tìm thấy sau thử nghiệm

Có thể không phải tất cả khiếm khuyết đều được phát hiện bằng các phương pháp kiểm tra sau hàn, ví dụ, kiểm tra trực quan, kiểm tra quang học tự động (AOI) hoặc kiểm tra bằng tia X.

Các khiếm khuyết được tìm thấy trong các kiểm tra này và có thể chắc chắn quy gán cho quy trình lắp ráp, phải được bao gồm khi xác định tỷ lệ ppm khiếm khuyết sau hàn.

Khi việc thử nghiệm điện tiến hành ngay sau khi hàn và không có kiểm tra trực quan, quang học hay bằng tia X nào tiếp theo trước khi làm lại hoặc loại bỏ, việc thu thập dữ liệu phải không được xem là có thể so sánh trực tiếp với dữ liệu thu được từ chuỗi quy trình mà trong đó hoạt động đầu tiên sau khi hàn là kiểm tra trực quan.

4.4. Phân loại khiếm khuyết

4.4.1. Nguồn gốc khiếm khuyết

Các khiếm khuyết sẽ được ghi nhận được phân chia theo các nguồn gốc khiếm khuyết dưới đây:

- áp kem hàn;

- áp keo dính;

- sắp đặt linh kiện;

- mối hàn.

Trong việc ghi nhận này, các khiếm khuyết có thể có về thiết kế, vật liệu và/hoặc quy trình, trước tiên được quy gán cho các nguồn gốc khiếm khuyết trên. Phân tích các dữ liệu ghi nhận được có thể dẫn tới việc phân chia tiếp thành các khiếm khuyết cho từng bước quy trình, các khiếm khuyết cho từng loại linh kiện, v.v.

4.4.2. Mẫu ghi nhận khiếm khuyết

Việc ghi nhận khiếm khuyết được thực hiện trên một mẫu được suy ra từ bản vẽ lắp ráp.

Các thông tin dưới đây phải được báo cáo trong mẫu đó:

- vị trí của khiếm khuyết;

- kiểu khiếm khuyết;

- số khiếm khuyết (ở vị trí liên quan);

- số tấm mạch in được kiểm tra.

Tùy thuộc vào mức độ của các khiếm khuyết, một mẫu có thể được sử dụng:

- cho từng tấm mạch in;

- cho từng lô sản phẩm;

- cho từng ngày sản xuất; hoặc

- từ một đơn vị sản xuất khác.

4.5. Gia công lại ngay trước khi hàn

Khi trình bày các khiếm khuyết hậu hàn, người lắp ráp phải nêu rõ liệu có thực hiện gia công lại giữa các công đoạn sắp xếp/lồng và hàn linh kiện.

4.6. Chủng loại dữ liệu khiếm khuyết

Khiếm khuyết ghi nhận được được chia thành hai chủng loại.

Chủng loại 1 gồm tổng số các khiếm khuyết sau hàn, bất kể nguồn gốc và bản chất. Dữ liệu này nhằm so sánh chung việc kiểm soát quy trình tổng thể tương đối và đầu ra chất lượng của các dây chuyền sản xuất khác nhau.

Đối với mục đích này,

a) Hàn được xác định là phát sinh từ hàn nóng chảy lại cả khối, nhúng cả khối (ví dụ gợn sóng, phun, kéo) và/hoặc hàn bằng tay;

b) Mặc dù một số khiếm khuyết sau hàn không liên quan đến mối hàn, (ví dụ, khiếm khuyết bảng mạch hoặc khiếm khuyết linh kiện), đường cơ sở dùng để tính dữ liệu ppm Chủng loại 1 là số các mối hàn nối trên tấm mạch in.

Chủng loại 2 bao gồm toàn bộ phần chính của dữ liệu liên quan đến trình tự toàn bộ quy trình. Phân tích các dữ liệu ghi nhận này có thể, ví dụ, dẫn đến việc phân chia thành khiếm khuyết cho từng bước quy trình, khiếm khuyết cho từng loại linh kiện. Trong bối cảnh này, các bước quy trình trước khi hàn được xác định là quy trình con. Các đường cơ sở dùng để tính dữ liệu ppm Chủng loại 2 thay đổi theo quy trình tham gia. Tham khảo phụ lục A

5. Xử lý dữ liệu

Dữ liệu thu được được dùng để xác định mức phần triệu (ppm) của khối sản xuất được kiểm tra. Mức ppm của lô sản xuất được định nghĩa là

| ppmsản phẩm = | Tổng số khiếm khuyết | x 106 |

| Tổng số mối hàn trong lô sản phẩm |

trong đó

tổng số khiếm khuyết bằng

• số khiếm khuyết tìm thấy trong quá trình kiểm tra 100 %

hoặc

| • số bảng mạch đã sản xuất x | số khiếm khuyết tìm thấy trong khi kiểm tra ngẫu nhiên |

| số bảng mạch đã kiểm tra |

tổng số mối hàn đã hàn bằng

• số bảng mạch đã sản xuất x số mối hàn trên mỗi bảng mạch.

Đối với phép kiểm tra ngẫu nhiên, công thức trên có hiệu lực với điều kiện độ tin cậy tính toán ppm phụ thuộc vào quy mô của kiểm tra ngẫu nhiên và mức ppm thực tế (xem phụ lục C). Vì lý do này, các mức ppm tính toán được từ kiểm tra ngẫu nhiên phải hoặc là bao gồm khoảng tin cậy hoặc là phải nêu số lượng mối hàn đã kiểm tra.

CHÚ THÍCH 1: Để có thể so sánh các sản phẩm khác nhau với nhau theo thời gian, dữ liệu cần được chuyển đổi sang cùng đơn vị thời gian.

CHÚ THÍCH 2: Tính toán mức ppm trung bình đối với việc sản xuất các loại tấm mạch in khác nhau (ví dụ A, B, C) được thực hiện như sau:

- tổng số khiếm khuyết hàn bằng

số khiếm khuyết trên loại A +

số khiếm khuyết trên loại B +

v.v.

- tổng số mối hàn bằng

số bảng mạch loại A đã sản xuất x số mối hàn trên loại A +

số bảng mạch loại B đã sản xuất x số mối hàn trên loại B +

v.v.

Phụ lục C bao hàm các ví dụ đã thực hiện.

6. Phân tích

Một cách để phân tích phần đóng góp vào tổng mức khiếm khuyết của các loại khiếm khuyết khác nhau là phương pháp phân tích Pareto. Ngoài việc phân chia thành các kiểu khiếm khuyết, cũng có thể phân chia thành, ví dụ, loại linh kiện. Phụ lục D nêu một ví dụ về cách thực hiện.

Phân chia theo khiếm khuyết có thể được sử dụng để phân tích (có thể tiếp tục phân chia) trường hợp mà các nguyên nhân có thể có bắt nguồn từ thiết kế, vật liệu, quy trình, v.v.

Nếu cần phải phân tích phần đóng góp của các quy trình phụ vào tổng mức khiếm khuyết, thì khi đó phải phân bổ cho các quy trình phụ cho việc xử lý các dữ liệu khiếm khuyết. Các nguyên nhân gây khiếm khuyết liên quan đến vật liệu và thiết kế có thể được xử lý theo cách tương ứng. Tuy nhiên, phân tích này đòi hỏi một sự hiểu biết toàn diện về quy trình chế tạo hoàn chỉnh. Các định nghĩa về các khiếm khuyết gây ra từ các quy trình phụ khác nhau được đưa ra trong IEC 61191-1, IEC 61191-2, IEC 61191-3, IEC 611914, IEC 61192-1, IEC 61192-2, IEC 61192-3 và IEC 61192-4. Một số khiếm khuyết đã được tổng hợp trong Phụ lục B.

Nếu chỉ phân tích các quy trình phụ, khi đó các khiếm khuyết phải được liên hệ với các công đoạn của các bước quy trình được thực hiện trong quy trình phụ đó (xem Phụ lục A).

Phân tích Pareto chỉ ra điểm mà kỹ sư quy trình cần tập trung hành động khắc phục vào đó. Để cải thiện mức chất lượng, các khiếm khuyết đóng góp lớn vào mức khiếm khuyết tổng phải được giải quyết trước tiên. Các khiếm khuyết đóng góp một phần nhỏ và dễ giải quyết cũng phải được xử lý. Mục tiêu luôn là đạt được mức khiếm khuyết càng thấp càng tốt.

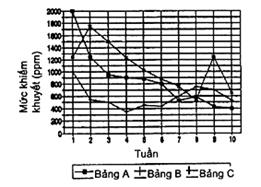

Có thể theo dõi mức ppm của một sản phẩm theo thời gian, nhờ đó phát hiện được các xu hướng. Các sản phẩm khác nhau có thể được so sánh với nhau, bằng cách sử dụng một đồ thị (mức ppm theo thời gian) và cung cấp một lược sử chất lượng hoàn chỉnh của hoạt động sản xuất. Hình D.5 cho một ví dụ cách thực hiện.

Theo dõi lịch sử tỷ lệ khiếm khuyết của sản phẩm qua một khoảng thời gian đáng kể cung cấp một chỉ báo về các điều kiện biên của việc chế tạo và mức chất lượng mà loại sản phẩm đó có thể được sản xuất thành công. Các điều kiện biên này, được xây dựng từ các dữ liệu kiểm soát quy trình liên quan tới thiết kế, vật liệu và các quy trình thuộc phạm vi áp dụng, cần được sử dụng để cải thiện các nguyên lý cơ bản về thiết kế sản phẩm. Điều này sẽ cho phép khởi động sản xuất các sản phẩm mới ở mức khiếm khuyết thấp.

Phụ lục A

(tham khảo)

Quy trình phụ

Bảng dưới đây đưa ra các mô tả khác nhau về các quy trình phụ.

Bảng A.1 - Mô tả các quy trình phụ

| Quy trình phụ | Đơn vị | Tiêu chí khiếm khuyết theo các bộ IEC 61191 và IEC 61192 | Liên quan đến tổng số các |

| Áp kem hàn | Chấm kem hàn | Chấm kem hàn bên ngoài quy định kỹ thuật quy trình | Chấm kem hàn |

| Sắp xếp SMC | Linh kiện | Sắp xếp linh kiện bên ngoài quy định kỹ thuật quy trình | Linh kiện |

| Hàn nóng chảy lại | Mối hàn | Mối hàn bên ngoài quy định kỹ thuật quy trình | Mối hàn |

| Hàn dán tự động HMC | Đầu cuối | Vị trí của đầu cuối bên ngoài quy định kỹ thuật quy trình | Đầu cuối |

| Áp keo dán | Chấm keo | Chấm keo bên ngoài quy định kỹ thuật quy trình | Chấm keo |

| Đặt SMC | Linh kiện | Sắp xếp linh kiện bên ngoài quy định kỹ thuật quy trình | Linh kiện |

| Lưu hóa keo | Mối gắn keo | Mối gắn keo bên ngoài quy định kỹ thuật quy trình | Mối gắn keo |

| Hàn dán HMC bằng tay | Đầu cuối | Vị trí của đầu cuối bên ngoài quy định kỹ thuật quy trình | Đầu cuối |

| Hàn sóng | Mối hàn | Mối hàn bên ngoài quy định kỹ thuật | Mối hàn |

| Quy trình tổng (sản phẩm) | Mối hàn | Mối nối ngoài quy định kỹ thuật | Mối hàn |

Mức độ khiếm khuyết được tính toán đối với các quy trình phụ bằng cách lấy tổng số các khiếm khuyết x 106 chi cho tổng số các đơn vị. Các giá trị này không nên xử lý bằng toán học với các giá trị quy trình phụ khác bởi vì không có cùng đơn vị. Cũng vì lý do đó, không thể xây dựng mối liên hệ toán học của mức ppm trung bình của tổng. Nếu cần xác định phần đóng góp của các quy trình phụ vào mức khiếm khuyết tổng, thì phải phân chia các quy trình phụ để xử lý các dữ liệu khiếm khuyết của sản phẩm hàn. Các khiếm khuyết phải được chuyển đổi sang các nguyên nhân khác nhau của quy trình phụ; nếu có thể, các nguyên do gây khiếm khuyết vật liệu và thiết kế cũng có thể được đưa vào. Phân tích này đòi hỏi một hiểu biết toàn diện về quy trình chế tạo hoàn chỉnh.

Chất lượng tổng thể của các mạch điện tử lắp ráp luôn được xác định bởi sản phẩm đã hàn.

Phụ lục B

(tham khảo)

Ví dụ về nhận định khiếm khuyết sản phẩm

|

|

|

|

| Một khiếm khuyết: Mối hàn bên phải có một đầu cuối thẳng và một lỗ trống trong chất hàn. | Một khiếm khuyết: Giữa một trong các dây đầu vào của linh kiện và vùng cần hàn dán, không có mối nối nào được tạo ra. | Hai khiếm khuyết: Hai trong số 10 mối nối hàn có lượng chất hàn quá ít. |

Hình B.1a - Không có hoặc không đủ chất hàn

|

|

|

|

| Một khiếm khuyết: Ở phía bên dưới, hai mối hàn đã chảy vào nhau | Một khiếm khuyết: Hai mối hàn đã chảy vào nhau. | Hai mươi năm khiếm khuyết: Các mối hàn liên quan đã chảy vào nhau. |

Hình B.1b - Dính mạch

|

|

|

|

| Một khiếm khuyết: Ở mối hàn bên trái của HMC, không thể nhận ra hình dạng của đầu cuối. | Hai khiếm khuyết: Chưa đến một nửa chiều rộng của linh kiện nằm trên vùng cần hàn dán | Tám mươi khiếm khuyết: Các dây đầu vào của linh kiện bị xê dịch đi hơn một nửa chiều rộng của dây đầu vào so với vùng cần hàn dán. |

Hình B.1c - Đặt chệch linh kiện

|

|

|

| Hai khiếm khuyết: Các mối nối đã không được thực hiện do linh kiện bị thiếu. | Tám mươi khiếm khuyết: Các mối nối đã không được thực hiện bởi linh kiện bị thiếu. |

Hình B.1d - Các linh kiện bị thiếu

Hình B.1 - Ghi nhận các khiếm khuyết

Phụ lục C

(tham khảo)

Ví dụ về cách tính toán

Bảng C.1 - Ví dụ 1 (kiểm tra 100 %)

| Kiểu tấm mạch in | Số tấm mạch in sản xuất | Số tấm mạch in kiểm tra | Số mối nối trên một tấm mạch in | Số khiếm khuyết tìm thấy trong 100% kiểm tra |

| D | 500 | 500 (=100 %) | 820 | 35 |

| E | 1 000 | 1 000 (=100 %) | 500 | 60 |

| F | 200 | 200 (=100 %) | 1 200 | 25 |

| D | 1 500 | 1 500 (=100 %) | 820 | 100 |

Mức ppm trung bình của tấm mạch in D:

- tổng số khiếm khuyết: 35 + 100 = 135

- tổng số mối nối: (500 x 820) + (1500 x 820) = 1640000

Mức ppm trung bình =

Mức ppm trung bình của tất cả tấm mạch in:

- tổng số khiếm khuyết: 35 + 60 + 25 + 100 = 220

- tổng số mối nối: (500 x 820) + (1000 x 500) + (200 x 1200) + (1500 x 820) = 2380000

Mức ppm trung bình =

Bảng C.2 - Ví dụ 2 (kiểm tra ngẫu nhiên)

| Kiểu tấm mạch in | Số tấm mạch in sản xuất | Số tấm mạch in kiểm tra | Số mối nối trên tấm mạch in | Số loại tìm thấy trong kiểm tra ngẫu nhiên |

| G | 500 | 50 (= 100 %) | 820 | 35 |

| H | 500 | 100 (= 20 %) | 500 | 60 |

| I | 100 | 50 (= 50 %) | 1 200 | 25 |

| G | 1 500 | 1 500 (= 100 %) | 820 | 100 |

Mức ppm trung bình của tấm mạch in G:

- tổng số khiếm khuyết:

- tổng số mối nối: (500 x 820) + (1500 x 820) = 1640000

Mức ppm trung bình =

Mức ppm trung bình của tất cả tấm mạch in:

- tổng số khiếm khuyết:

- tổng số mối nối: (500 x 820) + (1000 x 500) + (100 x 1200) + (1500 x 820) = 2010000

Mức ppm trung bình =

Phụ lục D

(tham khảo)

Ví dụ về cách ghi nhận khiếm khuyết và xử lý dữ liệu

Sản xuất các tấm mạch in loại A (ngày 01-07-1996)

Dữ liệu:

• số bảng mạch đã sản xuất: 100

• số linh kiện trên mỗi bảng mạch: 100

• số mối hàn trên mỗi bảng mạch: 1 000

Về việc ghi nhận khiếm khuyết, xem hình D.1.

Hình D.1 - Dữ liệu về ghi nhận khiếm khuyết

Dữ liệu về ghi nhận khiếm khuyết có thể phân tích bằng cách sử dụng nhiều cách phân loại khác nhau, ví dụ, phân loại thành loại khiếm khuyết và/hoặc loại linh kiện. Nếu đã rõ các nguyên nhân của khiếm khuyết là ở đâu, có thể phân loại khiếm khuyết theo vùng/nguyên nhân, ví dụ:

Thiết kế khuôn in áp QFP: 100 khiếm khuyết;

Quy trình in kem hàn SO: 50 khiếm khuyết;

Quy trình sắp xếp vị trí R/C: 20 khiếm khuyết;

Hỏng linh kiện PLCC: 30 khiếm khuyết.

Trong bảng dưới đây, ba phân vùng trong ví dụ trên đã được thực hiện:

Bảng D.1 - Ba phân vùng

| Phân tích kiểu khiếm khuyết | Phân tích kiểu linh kiện | Phân tích nguồn gốc | ||||||

| Kiểu | Số khiếm khuyết | % trong tổng | Kiểu | Số khiếm khuyết | % trong tổng | Vùng | Số khiếm khuyết | % trong tổng |

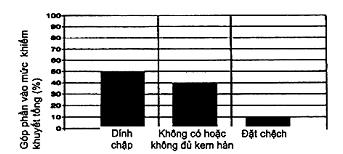

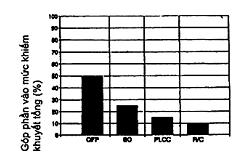

| Không có hoặc không đủ kem hàn | 80 | 40 | PLCC | 30 | 15 | Thiết kế | 100 | 50 |

| Dính chập | 100 | 50 | SO | 50 | 25 | Vật liệu | 30 | 15 |

| Đặt chệch | 20 | 10 | QFP | 100 | 50 | Quy trình | 50 + 20 | 35 |

|

|

|

| R/C | 20 | 10 |

|

|

|

| Tổng cộng | 200 | 100 |

| 200 | 100 |

| 200 | 100 |

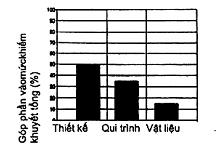

Dữ liệu có thể được biểu diễn bảng biểu đồ. Trong các hình D.2, D.3 và D.4, loại khiếm khuyết, loại linh kiện và nguồn gốc khiếm khuyết cùng với phần đóng góp vào mức khiếm khuyết tổng tính bằng phần trăm được vẽ lần lượt ở dạng đồ thị.

Hình D.2 - Phân chia theo loại khiếm khuyết

Hình D.3 - Phân chia theo loại linh kiện

Hình D.4 - Phân chia theo nguồn gốc khiếm khuyết

Có thể theo dõi mức chất lượng theo thời gian bằng cách vẽ đồ thị mức ppm theo các đơn vị sản xuất (tấm mạch in, lô, ngày). Trong hình D.5, mức chất lượng được thực hiện cho tấm mạch in A.

Hình D.5 - Mức ppm của tấm mạch in A, trong 10 ngày sản xuất vừa qua

Có thể thu thập dữ liệu của các sản phẩm khác nhau. Có thể thực hiện tổng quan về dữ liệu này theo thời gian. Để có thể so sánh các sản phẩm khác nhau với nhau theo thời gian, để có thể sử dụng, phải chuyển đổi các con số sang đơn vị thời gian. Hình D.6 cho một ví dụ.

Hình D.6 - Các mức ppm của việc sản xuất trên mỗi loại bảng mạch

MỤC LỤC

Lời nói đầu

1. Phạm vi áp dụng

2. Tài liệu viện dẫn

3. Thuật ngữ và định nghĩa

4. Ghi nhận khiếm khuyết

5. Xử lý dữ liệu

6. Phân tích

Phụ lục A (tham khảo) - Quy trình phụ

Phụ lục B (tham khảo) - Ví dụ về nhận định khiếm khuyết sản phẩm

Phụ lục C (tham khảo) - Ví dụ về cách tính toán

Phụ lục D (tham khảo) - Ví dụ về cách ghi nhận khiếm khuyết và xử lý dữ liệu

1 Dính mạch (ngắn mạch) là kết nối giữa các bộ phận kim loại được tạo ra bằng cách hàn không mong muốn và không yêu cầu trong việc thiết kế.

Bạn chưa Đăng nhập thành viên.

Đây là tiện ích dành cho tài khoản thành viên. Vui lòng Đăng nhập để xem chi tiết. Nếu chưa có tài khoản, vui lòng Đăng ký tại đây!

Tiêu chuẩn Việt Nam TCVN 10895-1:2015 PDF (Bản có dấu đỏ)

Tiêu chuẩn Việt Nam TCVN 10895-1:2015 PDF (Bản có dấu đỏ) Tiêu chuẩn Việt Nam TCVN 10895-1:2015 DOC (Bản Word)

Tiêu chuẩn Việt Nam TCVN 10895-1:2015 DOC (Bản Word)