- Tổng quan

- Nội dung

- Tiêu chuẩn liên quan

- Lược đồ

- Tải về

Tiêu chuẩn TCVN 9375:2012 Đặc tính kỹ thuật của giao diện nút mạng STM-N

| Số hiệu: | TCVN 9375:2012 | Loại văn bản: | Tiêu chuẩn Việt Nam |

| Cơ quan ban hành: | Bộ Khoa học và Công nghệ | Lĩnh vực: | Thông tin-Truyền thông |

|

Ngày ban hành:

Ngày ban hành là ngày, tháng, năm văn bản được thông qua hoặc ký ban hành.

|

2012 |

Hiệu lực:

|

Đã biết

|

| Người ký: | Đang cập nhật |

Tình trạng hiệu lực:

Cho biết trạng thái hiệu lực của văn bản đang tra cứu: Chưa áp dụng, Còn hiệu lực, Hết hiệu lực, Hết hiệu lực 1 phần; Đã sửa đổi, Đính chính hay Không còn phù hợp,...

|

Đã biết

|

TÓM TẮT TIÊU CHUẨN VIỆT NAM TCVN 9375:2012

Nội dung tóm tắt đang được cập nhật, Quý khách vui lòng quay lại sau!

Tải tiêu chuẩn Việt Nam TCVN 9375:2012

TIÊU CHUẨN QUỐC GIA

TCVN 9375:2012

MẠNG VIỄN THÔNG - GIAO DIỆN NÚT MẠNG STM-N THEO PHÂN CẤP SỐ ĐỒNG BỘ SDH - ĐẶC TÍNH KỸ THUẬT

Telecommunications network - STM-N network node interface for the synchronous digital hierarchy SDH - Technical Requirements

Lời nói đầu

TCVN 9375 : 2012 được xây dựng trên cơ sở tham khảo các khuyến nghị ITU-T G.707/Y.1322 và ITU-T G.780/Y.1351 của Liên minh Viễn thông Quốc tế ITU.

TCN 9375 : 2012 do Viện Khoa học kỹ thuật Bưu điện biên soạn, Bộ Thông tin và Truyền thông đề nghị, Tổng cục Tiêu chuẩn Đo lường Chất lượng thẩm định, Bộ Khoa học và Công nghệ công bố.

MẠNG VIỄN THÔNG - GIAO DIỆN NÚT MẠNG STM-N THEO PHÂN CẤP SỐ ĐỒNG BỘ SDH - ĐẶC TÍNH KỸ THUẬT

Telecommunications network - STM-N network node interface for the synchronous digital hierarchy SDH - Technical Requirements

1. Phạm vi áp dụng

Tiêu chuẩn này đưa ra các yêu cầu đối với các tín hiệu STM-N tại giao diện nút mạng (NNI) của mạng phân cấp số đồng bộ (SDH), bao gồm:

- Cấu trúc khung STM-N

- Cấu trúc ghép kênh và sắp xếp tín hiệu nhánh vào VC-n

- Con trỏ và các byte mào đầu

- Liên kết các container ảo VC-n

Tiêu chuẩn này làm sở cứ cho việc đánh giá, đảm bảo kết nối giữa các thiết bị và giữa các mạng SDH/NG-SDH.

2. Tài liệu viện dẫn

Các tài liệu viện dẫn sau đây là cần thiết để áp dụng tiêu chuẩn này. Đối với các tài liệu viện dẫn ghi năm công bố thì áp dụng phiên bản được nêu. Đối với các tài liệu viện dẫn không ghi năm công bố thì áp dụng phiên bản mới nhất, bao gồm cả các sửa đổi, bổ sung (nếu có).

ITU-T Recommendation G.691 (2006), Optical interfaces for single-channel STM-64 and other SDH systems with optical amplifiers (Giao diện quang cho các hệ thống đơn kênh STM-64 và các hệ thống SDH khác có sử dụng khuếch đại quang)

ITU-T Recommendation G.702 (1988), Digital hierarchy bit rates (Các phân cấp số đồng bộ).

ITU-T Recommendation G.703 (2001), Physical/electrical characteristics of hierarchical digital interfaces (Đặc tính điện/vật lý của các giao diện phân cấp số).

ITU-T Recommendation G.704 (1998), Synchronous frame structures used at 1544, 6312, 2048, 8448 and 44 736 kbit/s hierarchical levels (Cấu trúc khung đồng bộ tại các phân cấp số 1544, 6312, 2048, 8448 và 44 736 kbit/s)

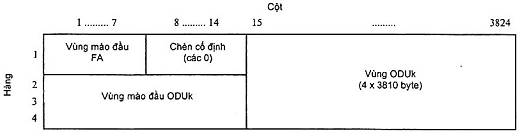

ITU-T Recommendation G.709/Y.1331 (2003), Interfaces for the Optical Transport Network (OTN) (Giao diện mạng truyền tải quang (OTN)).

ITU-T Recommendation G.780/Y.1351 (2004), Terms and definitions for synchronous digital hierarchy (SDH) networks (Khái niệm và định nghĩa đối với các mạng phân cấp số đồng bộ (SDH)).

ITU-T Recommendation G.783 (2006), Characteristics of synchronous digital hierarchy (SDH) equipment functional blocks (Đặc tính của các khối thiết bị chức năng phân cấp số đồng bộ (SDH)).

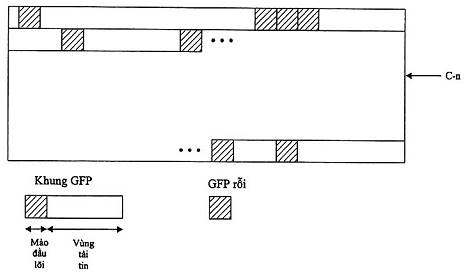

ITU-T Recommendation G.7041/Y.1303 (2005), Generic framing procedure (GFP) (Thủ tục định khung chung (GFP)).

ITU-T Recommendation G.7042/Y.1305 (2006), Link capacity adjustment scheme (LCAS) for virtual concatenated signals (Cơ chế điều chỉnh dung lượng tuyến (LCAS) đối với các tín hiệu ghép ảo).

ITU-T Recommendation G.802 (1988), Interworking between networks based ono different digital hierarchies and speech encoding laws (Liên kết giữa các có phân cấp số khác nhau và các luật mã hóa tiếng nói).

ITU-T Recommendation G.803 (2000), Architecture of transport networks based on the synchronous digital hierarchy (SDH) (Cấu trúc của các mạng truyền tải theo phân cấp số đồng bộ (SDH)).

ITU-T Recommendation G.806 (2006), Characteristics of transport equipment - Description methodology and generic functionality (Đặc tính của thiết bị truyền tải - Phương pháp luận mô tả và chức năng chung).

ITU-T Recommendation G.831 (2000), Management capabilities of transport networks based on the synchronous digital hierarchy (SDH) (Năng lực quản lý của các mạng truyền tải theo phân cấp số đồng bộ).

ITU-T Recommendation G.841 (1998), Types and characteristics of SDH network protection architectures (Loại và đặc tính của các kiến trúc bảo vệ mạng SDH).

ITU-T Recommendation G.957 (2006), Optical interfaces for equipments and systems relating to the synchronous digital hierarchy (Giao diện quang đối với các thiết bị và hệ thống theo phân cấp số đồng bộ).

ITU-T Recommendation G.984.3 (2004), Gigabit-capable Passive Optical Networks (G-PON): Transmission convergence layer specifications (Mạng quang thụ động gigabit (G-PON): Các chỉ tiêu lớp hội tụ truyền tải).

ITU-T Recommendation G.991.2 (2003), Single-pair high-speed digital subscriber line (SHDSL) transceivers (Các bộ thu đường thuê bao số một dây tốc độ cao (SHDSL)).

ITU-T Recommendation I.432.1 (1999), B-ISDN user-network interface - Physical layer specification: General characteristics (Giao diện thuê bao-mạng B-ISDN - Đặc tính lớp vật lý: Đặc tính chung).

ITU-T Recommendation I.432.2 (1999), B-ISDN user-network interface - Physical layer specification: 155 520 kbit/s and 622 080 kbit/s operation (Giao diện thuê bao-mạng B-ISDN - Đặc tính lớp vật lý: tốc độ 155 520 kbit/s và 622 080 kbit/s).

ITU-T Recommendation O.181 (2002), Equipment to assess error performance on STM-N interfaces (Thiết bị dung để đánh giá chất lượng lỗi tại các giao diện STM-N).

ITU-T Recommendation Q.921 (1997), ISDN user-network interface - Data link layer specification (Giao diện thuê bao-mạng ISDN - Đặc tính lớp tuyến dữ liệu).

ITU-R Recommendation F.750-4 (2000), Architectures and functional aspects of radio-relay systems for synchronous digital hierarchy (SDH)-based networks (Kiến trúc và các khía cạnh chức năng của các hệ thống chuyển tiếp vô tuyến dành cho các mạng phân cấp số đồng bộ (SDH)).

ITU-R Recommendation S.1149-2 (2005), Network architecture and equipment functional aspects of digital satellite systems in the fixed-satellite service forming part of synchronous digital hierarchy transport networks (Kiến trúc mạng và các khía cạnh chức năng thiết bị của các hệ thống vệ tinh số cung cấp dịch vụ vệ tinh cố định hình thành phần mạng truyền tải theo phân cấp số).

ETSI ETS 300 216 (1992), Network Aspects (NA); Metropolitan Area Network (MAN); Physical layer convergence procedure for 155,520 Mbit/s (Các khía cạnh về mạng (NA); Mạng đô thị (MAN); Cơ chế hội tụ lớp vật lý đối với tốc độ 155,520 Mbit/s).

IEEE Standard 802.3 (2005), Information technology - Telecommunications and information exchange between systems - Local and metropolitan area networks - Specific requirements Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications Amendment: Media Access Control (MAC) Parameters, Physical Layers, and Management Parameters for 10 Gb/s Operation (Công nghệ thông tin - Trao đổi thông tin và viễn thông giữa các hệ thống - Mạng nội hạt và đô thị - Các yêu cầu cụ thể Phần 3: Phương pháp đa truy nhập theo sóng mạng có phát hiện xung đột (CSMA/CD) và các đặc tính lớp vật lý: Các tham số điều khiển truy nhập môi trường (MAC), lớp vật lý và các tham số quản lý đối với tốc độ 10Gb/s).

3. Thuật ngữ và định nghĩa

3.1

Chẵn lẻ luân phân theo bit -X (Bit Interleaved Parity-X):

Phương pháp dùng để giám sát lỗi. Với chẵn lẻ dương, mã bit-X được sinh ra bởi thiết bị phát trên một phần nhất định nào đó của tín hiệu theo phương thức sao cho bit đầu tiên của mã sẽ cho chẵn lẻ dương trên bit đầu tiên của tất cả các chuỗi gồm X-bit nằm trong phần kiểm soát của tín hiệu, bit thứ hai cho chẵn lẻ dương trên bit thứ hai của tất cả các chuỗi gồm X-bit nằm trong phần nhất định nào đó, vân vân… Chẵn lẻ dương được sinh ra bằng cách đặt các bit BIP-X sao cho sẽ có một số chẵn các bit 1 trong mỗi phần được giám sát của tín hiệu. Mỗi phần được giám sát sẽ chứa tất cả các bit nằm ở cùng một vị trí bit trong các chuỗi gồm X-bit thuộc phần kiểm soát của tín hiệu. Phần kiểm soát gồm cả BIP-X.

3.2

Con trỏ (pointer)

Bộ chỉ báo để chỉ ra độ lệch khung của một container ảo so với chuẩn khung của thực thể truyền tải mà container ảo được truyền dẫn trên đó.

3.3

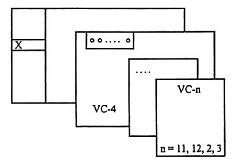

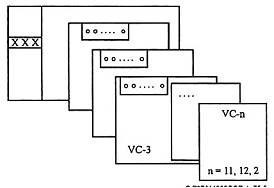

Container ảo - n (virtual container-n):

Cấu trúc thông tin được sử dụng cho kết nối lớp luồng trong SDH. Nó bao gồm phần tải tin và thông tin POH được tổ chức thành cấu trúc khung theo khối, các khung này được lặp lại sau mỗi chu kỳ 125 hoặc 500 ms. Thông tin để xác định điểm bắt đầu của khung VC-n được cung cấp bởi lớp mạng server. Có hai loại container ảo được định nghĩa:

- Container ảo bậc thấp VC-n (n = 11, 12, 2, 3): VC-n bao gồm một container-n và cùng với phần mào đầu luồng POH tương ứng.

- Container ảo bậc cao VC-n (n = 3, 4): VC-n bao gồm một container-n (n = 3, 4) hoặc nhóm TUG (TUG-2 hoặc TUG-3) cùng với phần mào đầu luồng POH tương ứng.

3.4

Container-n (n = 11, 12, 2, 3, 4) (container-n):

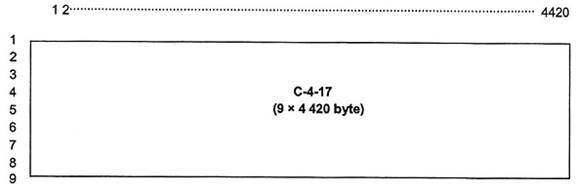

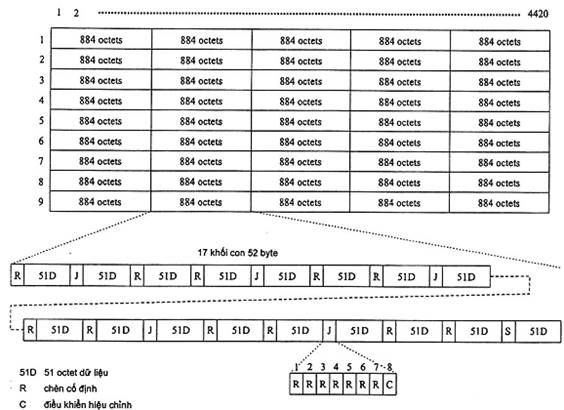

Cấu trúc thông tin tạo nên tải tin đồng bộ cho container ảo. Đối với mỗi container ảo xác định sẽ có một container tương ứng. Một số hữu hạn các container tiêu chuẩn đã được xác định và có chức năng thích ứng các tốc độ mạng thông dụng. Các tốc độ này hiện đang được quy định trong G.702.

3.5

Đa thức sinh (generator polynomial):

Đa thức được sử dụng cho việc mã hóa các loại mã vòng. Phần còn lại sau khi chia đa thức thông tin cho đa thức sinh sẽ là phân dư của từ mã được mã hóa.

3.6

Đồng chỉnh SDH (SDH aligning):

Thủ tục mà thông tin bù khung được đưa vào khối nhánh hoặc khối giám sát khi thích ứng vào khung tương ứng của lớp tương ứng.

3.7 Ghép kênh SDH (SDH multiplexing):

Thủ tục ghép mà ở đó các luồng tín hiệu bậc thấp được thích ứng vào một luồng bậc cao hoặc ghép các luồng tín hiệu bậc cao vào tín hiệu STM-N.

3.8

Giao diện dSTM-12NMi (dSTM-12NMi interface):

Giao diện truyền dẫn SDH truyền tải một hoặc nhiều TU-12 với phần mào đầu đoạn dựa trên SHDSL. Giao diện dSTM-12NMi được định nghĩa cho công nghệ truyền tải SHDSL. Số N của TU-12 trong giao diện dSTM-12NMi quy định trong tiêu chuẩn này nằm trong giới hạn từ 1 đến 9. Số M của SHDSL là số đôi dây mà tín hiệu dSTM-12NMi truyền trên đó (M = 1 + 4). Số i thể hiện việc có hoặc không có của kênh DCC (M x i x 8) kbit/s trong tín hiệu dSTM-12NMi. i = 0, 1, …, 7 trong trường hợp một đôi dây; i = 0,…, 4 trong trường hợp hai đôi dây; i = 0,…, 3 trong trường hợp ba đôi dây; i = 0, 1, 2 trong trường hợp bốn đôi dây hoặc bằng 1. Quy định về N va M xem trong Bảng G.1 của tiêu chuẩn này.

3.9

Giao diện gSTM-11 (gSTM-11 Interface):

Giao diện truyền dẫn SDH tải một TU-11 với phần mào đầu dựa trên G-PON, Giao diện gSTM-11 được định nghĩa cho công nghệ truyền tải G-PON. Xem Bảng H.1.

3.10

Giao diện gSTM-12 (gSTM-12 Interface):

Giao diện truyền dẫn SDH tải một TU-12 với phần mào đầu dựa trên G-PON, Giao diện gSTM-12 được định nghĩa cho công nghệ truyền tải G-PON. Xem Bảng H.1.

3.11

Giao diện gSTM-2 (gSTM-2 Interface):

Giao diện truyền dẫn SDH tải một TU-2 với phần mào đầu dựa trên G-PON, Giao diện gSTM-2 được định nghĩa cho công nghệ truyền tải G-PON. Xem Bảng H.1.

3.12

Giao diện gSTM-3 (gSTM-3 Interface):

Giao diện truyền dẫn SDH tải một TU-3 với phần mào đầu dựa trên G-PON, Giao diện gSTM-3 được định nghĩa cho công nghệ truyền tải G-PON. Xem Bảng H.1.

3.13

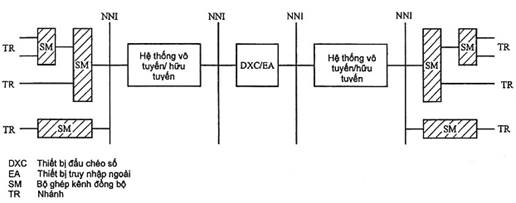

Giao diện nút mạng (NNI) (network node interface):

Giao diện được sử dụng để kết nối với nút mạng khác. Trên Hình 1 minh họa vị trí của các NNI trong mạng.

Hình 1 - Vị trí của NNI

3.14

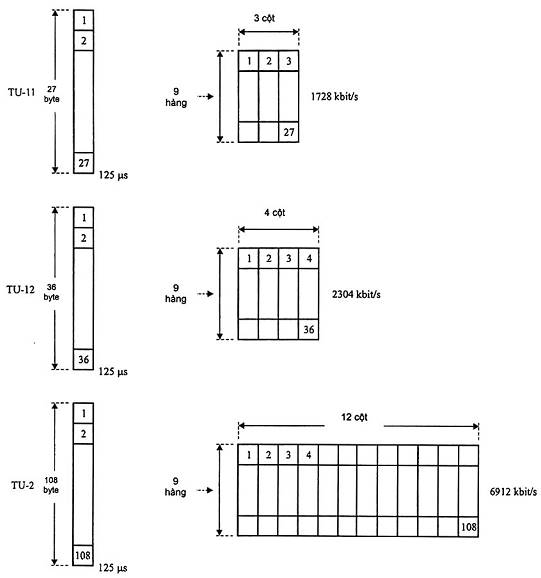

Khối nhánh (TU-n) (tributary unit-n):

Cấu trúc thông tin cung cấp sự tương thích giữa lớp luồng bậc thấp và lớp luồng bậc cao. Nó bao gồm phần tải tin (container ảo bậc thấp) và con trỏ khối nhánh. Con trỏ này chỉ ra độ bù giữa vị trí bắt đầu của khung tải tin so với vị trí bắt đầu của khung container ảo bậc cao.

TU-n (n = 11, 12, 2, 3, 4) gồm có một VC-n cùng với một con trỏ TU-n.

3.15

Khối quản lý -n (AU-n) (administrative unit-n):

Cấu trúc thông tin để cung cấp sự thích ứng giữa lớp luồng bậc cao và lớp đoạn ghép kênh. Nó bao gồm phần tải tin (container ảo bậc cao) và con trỏ khối quản lý. Con trỏ này sẽ chỉ ra độ bù của vị trí bắt đầu của khung tải so với điểm bắt đầu của khung đoạn ghép kênh. Có hai loại khối quản lý được định nghĩa:

- AU-4 bao gồm có VC-4 và con trỏ khối quản lý. Con trỏ này có chức năng đồng chỉnh pha của VC-4 với khung STM-N.

- AU-3 gồm có VC-3 và con trỏ khối quản lý. Con trỏ này có chức năng đồng chỉnh pha của VC-3 với khung STM-N.

Trong mỗi trường hợp, vị trí của con trỏ khối quản lý là cố định so với khung STM-N.

3.16

Liên kết (concatenation):

Thủ tục ghép băng thông của một số các container nhỏ hơn vào một container có băng thông lớn hơn. Có hai kiểu liên kết:

- Liên kết liên tục: duy trì độ rộng băng thông liên tục trong suốt quá trình chuyển tải. Liên kết liên tục yêu cầu chức năng liên kết tại từng phần tử mạng.

- Liên kết ảo: chia băng thông liên tục thành các VC, chuyển tải từng VC và tái tổ hợp các VC này thành băng thông liên tục tại điểm cuối của truyền dẫn. Liên kết ảo chỉ yêu cầu chức năng liên kết tại thiết bị kết cuối luồng truyền dẫn.

3.17

Mã hệ thống (systematic code):

Các bit dữ liệu gốc dùng cho mã nhị phân không bị thay đổi trong quá trình mã hóa. Các bit hoặc các ký hiệu dư được thêm vào từng khối mã một cách riêng biệt.

3.18

Mã nhị phân rút gọn-BCH (shortened binary-BCH):

Phiên bản rút gọn của mã vòng tuyến tính khối. Mã nhị phân rút gọn BCH có các đặc tính chung sau:

n = 2m - 1 - s

k = n - t x m

d = 2 x t + 1

trong đó:

n là kích thước của toàn bộ từ mã;

k là số các bit thông tin;

m là tham số của mã BCH;

t là số các lỗi được sửa trong khối của mã BCH;

d là khoảng cách mã tối thiểu;

s là lượng thông tin bị loại trừ như là phần rút gọn của mã

3.19

Modul truyền tải đồng bộ (STM) (synchronous transport module):

Cấu trúc thông tin được dùng để cung cấp các kết nối lớp phân đoạn trong SDH. STM bao gồm phần tải thông tin và thông tin mào đầu đoạn (SOH) được tổ chức thành cấu trúc khung theo khối, được lặp lại sau mỗi chu kỳ 125 ms. STM cơ sở được định nghĩa tại tốc độ 155 520 kbit/s và được gọi là STM-1. Các STM có dung lượng cao hơn có tốc độ bit bằng N lần STM-1 (N = 4, 16, 64, 256). Các giá trị N lớn hơn còn đang được nghiên cứu.

STM-0 bao gồm một khối quản lý ở mức 3. STM-N, N ³ 1 gồm có một nhóm khối quản lý ở mức N (AUG-N) cùng với SOH. Tốc độ bít của các phân cấp STM-N được quy định trong Bảng 2 của tiêu chuẩn này.

3.20

Nhóm khối nhánh (TUG) (tributary unit group):

Một hoặc nhiều khối nhánh có vị trí xác định cố định trong tải VC-n bậc cao. TUG-2 bao gồm một tổ hợp đồng nhất các TU-11, TU-12 hoặc TU-2, TUG-3 bao gồm một tổ hợp đồng nhất các TUG-2 hoặc TU-3.

3.21

Nhóm khối quản lý (AUG) (administrative unit group):

Một hoặc nhiều khối quản lý chiếm giữ một vị trí cố định đã được xác định trước trong phần tải tin của STM.

AUG-1 gồm có một tổ hợp đồng nhất các AU-3 hoặc một AU-4.

3.22

Phân cấp số đồng bộ (SDH) (synchronous digital hierarchy):

Tập hợp phân cấp của các cấu trúc truyền tải số được chuẩn hóa để truyền tải các thông tin một cách thích ứng trên các mạng truyền dẫn vật lý.

3.23

Ánh xạ SDH (SDH mapping):

Thủ tục nhằm thích ứng các tín hiệu nhánh vào các VC ở phần biên của mạng SDH.

4. Ký hiệu và thuật ngữ

| Ký hiệu | Tiếng Việt |

| AIS API APS ATM AU-n AUG-N BCH BER BIP-X C-n CAS CRC-N DCC DQDB DNU dSTM EOS FCS FDDI FEBE FEC FERF FSI GEM GID gSTM HDLC HEC HOVC IEC IP ISF ISDN ISID LAPD LAPS LCAS LCD LOP LOVC LSB MAN MFI MSB MS-AIS MSF-AIS MSOH MS-RDI MS-REI MST MSTE NDF NNI NORM ODI ODUk OEI OH OPUk OTN OTUk PDH PLM POH PPP PTE PTR RDI REI RFI RS-Ack RSOH SD SDH SLM SOH SQ SSU STM(-N) TCM TC-RDI TC-REI TCOH TCT TCTE TIM TSID TTI TU-n TUG(-n) UNEQ VC-n VC-n-X VC-n-Xc VC-n-Xv VCG WAN | Tín hiệu chỉ thị cảnh báo Nhận dạng điểm truy cập Chuyển mạch bảo vệ tự động Phương thức truyền tải không đồng bộ Khối quản lý - n Nhóm khối quản lý - N Mã BCH sửa lỗi bậc 3 Tỷ lệ lỗi bit Chẵn lẻ luân phiên theo bit - X Container-n Báo hiệu kênh riêng Kiểm tra mã dự vòng độ rộng N. Từ điều khiển CTRL được gửi từ nguồn đến nơi thu Kênh thông tin số liệu Bus hai hàng đợi phân bố Không sử dụng Module truyền tải đồng bộ dựa trên SHDSL Điểm cuối của chuỗi Chuỗi kiểm tra khung Giao diện dữ liệu phân bố sợi quang Lỗi khối đầu xa (được đổi thành REI) Sửa lỗi trước Sự cố thu đầu xa Chỉ thị trạng thái FEC Phương pháp đóng gói G-PON Nhận dạng nhóm Chế độ truyền tải đồng bộ dựa trên GEM Điều khiển tuyến dữ liệu bậc cao Điền khiển lỗi phần mào đầu Container ảo bậc cao Đếm lỗi bit đến Giao thức Internet Sự cố tín hiệu đến Mạng số dịch vụ tích hợp Nhận dạng tín hiệu rỗi Giao thức truy nhập tuyến cho kênh D Thủ tục truy nhập tuyến - SDH Cơ chế điều chỉnh dung lượng tuyến Mất phân định tế bào Mất con trỏ Container ảo bậc thấp Bít có ý nghĩa tối thiểu Mạng đô thị Chỉ thị đa khung Bít có ý nghĩa nhất Tín hiệu chỉ thị cảnh báo đoạn ghép kênh Tín hiệu chỉ thị cảnh báo FEC đoạn ghép kênh Mào đầu đoạn ghép kênh Chỉ thị sai hỏng đầu xa đoạn ghép kênh Chỉ thị lỗi đầu xa đoạn ghép kênh Trạng thái thành viên Thiết bị đầu cuối đoạn ghép kênh Cờ dữ liệu mới Giao diện nút mạng Chế độ làm việc bình thường Chỉ thị sai hỏng tại tín hiệu ra Khối dữ liệu kênh quang - k Chỉ thị lỗi tại tín hiệu ra Mào đầu Khối tải kênh quang - k Mạng truyền tải quang Khối truyền tải kênh quang - k Phân cấp số cận đồng bộ Sự không phù hợp về tải Mào đầu luồng Giao thức điểm - điểm Phần tử kết cuối luồng Con trỏ Chỉ thị sai hỏng đầu xa Chỉ thị lỗi đầu xa Chỉ thị sự cố đầu xa Báo truyền lại chuỗi Mào đầu đoạn trạm lặp Suy giảm tín hiệu Phân cấp số đồng bộ Sự không phù hợp về nhãn tín hiệu Mào đầu đoạn Chỉ thị chuỗi Thiết bị cung cấp nguồn đồng bộ Module truyền tải đồng bộ (-N) Giám sát kết nối chuyển tiếp Chỉ thị sai hỏng kết nối chuyển tiếp Chỉ thị lỗi đầu xa của kết nối chuyển tiếp Mào đầu kết nối chuyển tiếp Vết của kết nối chuyển tiếp Thiết bị đầu cuối của kết nối chuyển tiếp Sự không phù hợp về nhận dạng vết Nhận dạng tín hiệu đo thử Nhận dạng vết Khối nhánh - n Nhóm khối nhánh - n Không sẵn sàng Container ảo - n X container ảo - n X container ảo - n liên kết liên tục X container ảo - n liên kết ảo Nhóm liên kết ảo Mạng diện rộng |

5. Yêu cầu kỹ thuật cho nguyên lý ghép kênh cơ bản

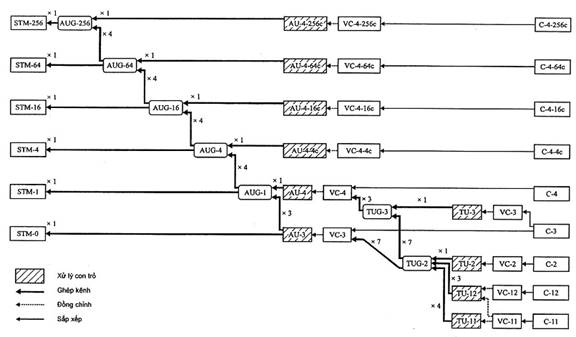

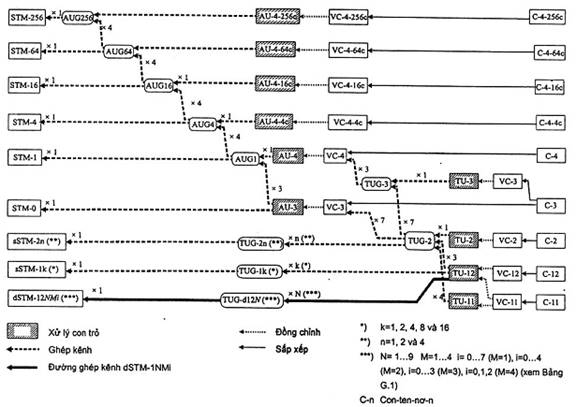

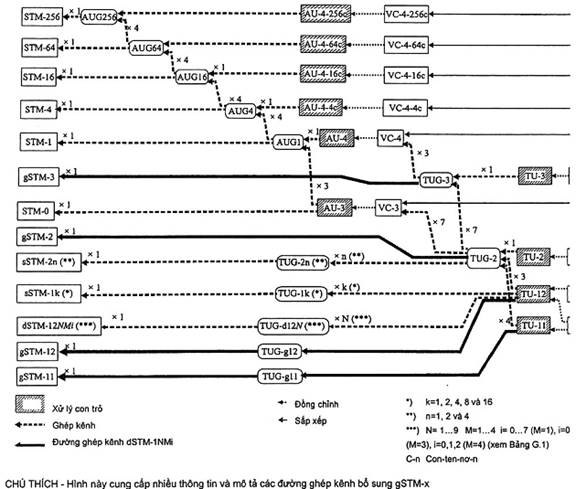

5.1 Cấu trúc ghép kênh

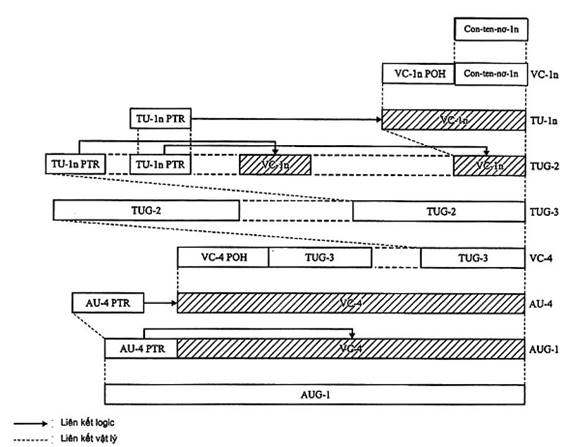

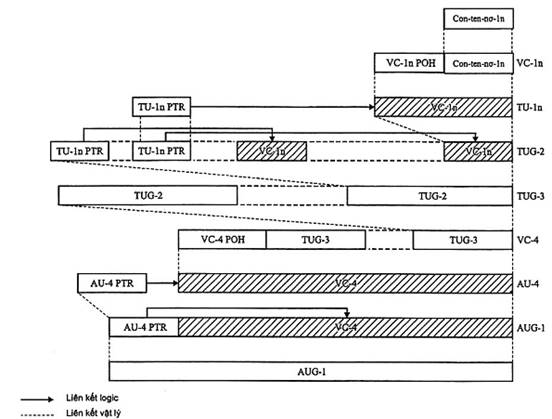

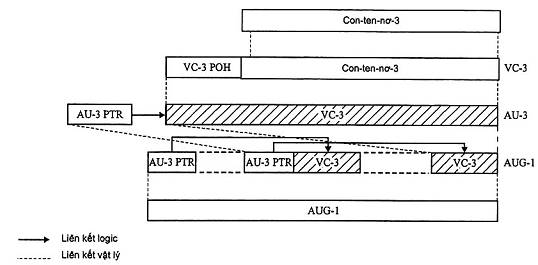

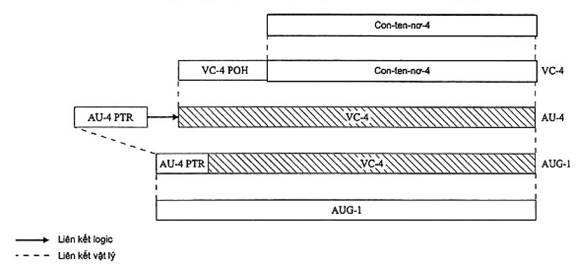

Phương pháp để ghép các tín hiệu bậc thấp vào các luồng SDH được quy định trên các Hình 2, Hình 3, Hình 4, Hình 5 và Hình 6.

CHÚ THÍCH - VC-4-Xc tốc độ cao có thể được sử dụng mà không cần bất kỳ một ràng buộc nào trong kết nối điểm - điểm. Mạng SDH có thể bị giới hạn trong phạm vi tốc độ bit VC-4-Xc nhất định (ví dụ X £ 64) vì ring MS SPRING phải dành 50% băng tần STM-N cho việc bảo vệ.

Bảng 1 - Loại VC và dung lượng

| Loại VC | Băng tần VC | Tải VC |

| VC-11 | 1 664 kbit/s | 1 600 kbit/s |

| VC-12 | 2 240 kbit/s | 2 176 kbit/s |

| VC-2 | 6 848 kbit/s | 6 784 kbit/s |

| VC-3 | 48 960 kbit/s | 48 384 kbit/s |

| VC-4 | 150 336 kbit/s | 149 760 kbit/s |

| VC-4-4c | 601 344 kbit/s | 599 040 kbit/s |

| VC-4-16c | 2 405 376 kbit/s | 2 396 160 kbit/s |

| VC-4-64c | 9 621 504 kbit/s | 9 584 640 kbit/s |

| VC-4-256c | 38 486 016 kbit/s | 38 338 560 kbit/s |

Hình 2 - Cấu trúc ghép kênh

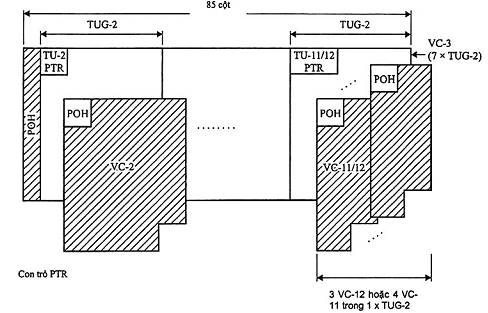

CHÚ THÍCH 1 - Phần không gạch chéo là phần đồng chỉnh pha. Đồng chỉnh pha giữa phần không gạch chéo và phần gạch chéo được xác định bởi con trỏ (PTR) và được chỉ ra bởi mũi tên

CHÚ THÍCH 2 - n=1, 2

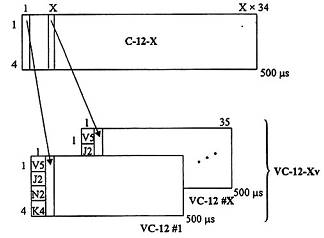

Hình 3 - Phương pháp ghép kênh trực tiếp từ container-11/container-12 sử dụng AU-4

CHÚ THÍCH 1 - Phần không gạch chéo là phần đồng chỉnh pha. Đồng chỉnh pha giữa phần không gạch chéo và phần gạch chéo được xác định bởi con trỏ (PTR) và được chỉ ra bởi mũi tên

CHÚ THÍCH 2 - n=1, 2

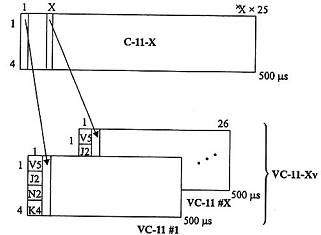

Hình 4 - Phương pháp ghép kênh trực tiếp từ container-11/container-12 sử dụng AU-3

CHÚ THÍCH - Phần không gạch chéo là phần đồng chỉnh pha. Đồng chỉnh pha giữa phần không gạch chéo và phần gạch chéo được xác định bởi con trỏ (PTR) và được chỉ ra bởi mũi tên

Hình 5 - Phương pháp ghép kênh trực tiếp từ container-3 sử dụng AU-3

CHÚ THÍCH - Phần không gạch chéo là phần đồng chỉnh pha. Đồng chỉnh pha giữa phần không gạch chéo và phần gạch chéo được xác định bởi con trỏ (PTR) và được chỉ ra bởi mũi tên

Hình 6 - Phương pháp ghép kênh trực tiếp từ container-4 sử dụng AU-4

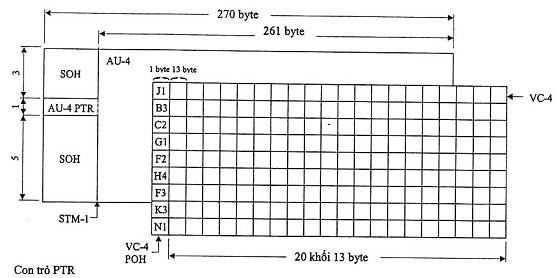

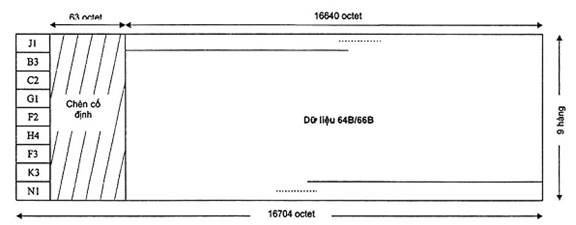

5.2 Cấu trúc khung cơ sở

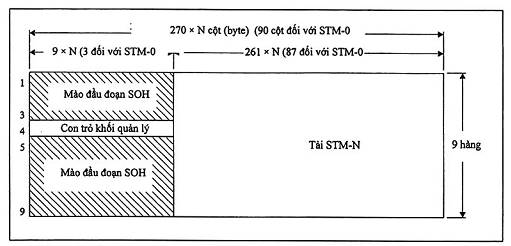

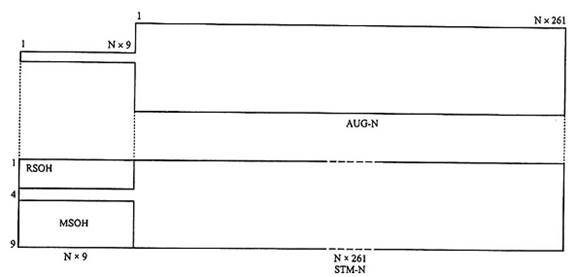

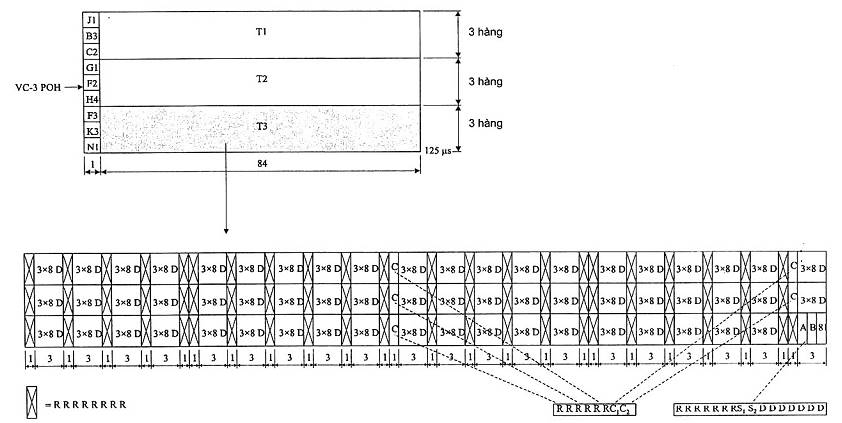

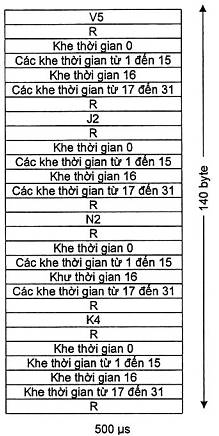

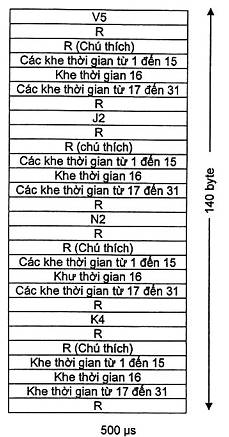

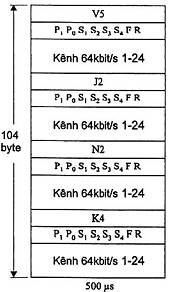

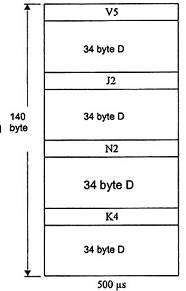

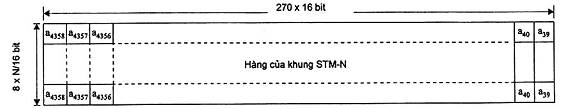

Cấu trúc khung của tín hiệu STM-N được quy định trên Hình 7, bao gồm 3 phần chính:

- Thông tin mào đầu đoạn (SOH)

- Con trỏ khối quản lý

- Tải tin

Hình 7 - Cấu trúc khung STM-N

5.2.1 Thông tin mào đầu đoạn

Hàng 1-3 và 5-9 của cột 1 đến 9xN trong khung STM-N trên Hình 7 là được dành cho SOH. Phân bổ dung lượng và chi tiết về các chức năng của SOH được trình bày trong điều 8.

5.2.2 Các con trỏ khối quản lý

Hàng 4 của cột từ 1 đến 9xN trong Hình 7 được dành cho con trỏ khối quản lý. Ứng dụng và các yêu cầu cụ thể đối với con trỏ được trình bày trong điều 8.

5.2.3 Các khối quản lý trong STM-N

Phần tải tin của STM-N được dùng để tải một AUG-N, trong đó:

a) AUG-256 có thể bao gồm 4 AUG-64 hoặc 1 AU-4-256c.

b) AUG-64 có thể bao gồm 4 AUG-16 hoặc 1 AU-4-64c.

c) AUG-16 có thể bao gồm 4 AUG-4 hoặc 1 AU-4-16c.

d) AUG-4 có thể bao gồm 4 AUG-1 hoặc 1 AU-4-4c.

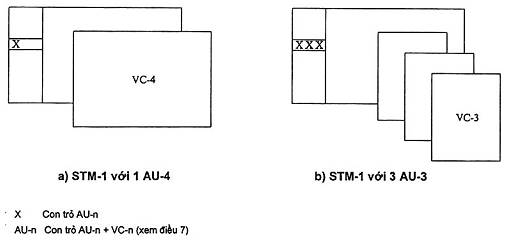

e) AUG-1 có thể bao gồm 1 AU-4 hoặc 3 AU-3s.

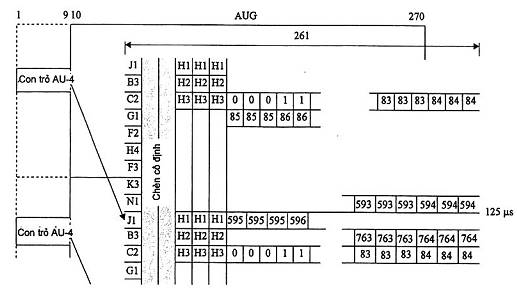

VC-n tương ứng với mỗi AU-n có pha không cố định so với khung STM-N. Vị trí byte đầu tiên của VC-n được chỉ ra bởi con trỏ AU-n. Con trỏ AU-n nằm ở vị trí cố định trong khung STM-N (xem minh họa trong các hình từ Hình 3 đến Hình 9).

Thông qua VC-4, AU-4 có thể được sử dụng để tải các TU-n (n=11, 12, 2, 3) tạo nên ghép kênh 2 cấp (xem minh họa trên các Hình 8a và Hình 9a) VC-n tương ứng với mỗi TU-n không có quan hệ về pha cố định so với điểm bắt đầu của VC-4. Con trỏ TU-n nằm ở vị trí cố định trong khung VC-4 và chỉ ra vị trí byte đầu tiên của VC-n trong khung VC-4.

Thông qua VC-3, AU-3 có thể được sử dụng để tải các TU-n (n=11, 12, 2, 3) tạo nên ghép kênh 2 cấp (xem minh họa trên Hình 8b và Hình 9b). VC-n tương ứng với mỗi TU-n không có quan hệ về pha cố định so với điểm bắt đầu của VC-3. Con trỏ TU-n nằm ở vị trí cố định trong khung VC-3 và chỉ ra vị trí byte đầu tiên của VC-n trong khung VC-3.

Hình 8 - Khối quản lý trong khung STM-1

|

a) STM-1 với 1 AU-4 chứa các TU |

b) STM-1 với 3 AU-3 chứa các TU |

X Con trỏ AU-n

o Con trỏ TU-n

AU-n Con trỏ AU-n + VC-n (xem điều 7)

TU-n Con trỏ TU-n + VC-n (xem điều 7)

Hình 9 - Ghép kênh 2 cấp

5.2.4 Tín hiệu bảo dưỡng

5.2.4.1 Tín hiệu chỉ thị cảnh báo

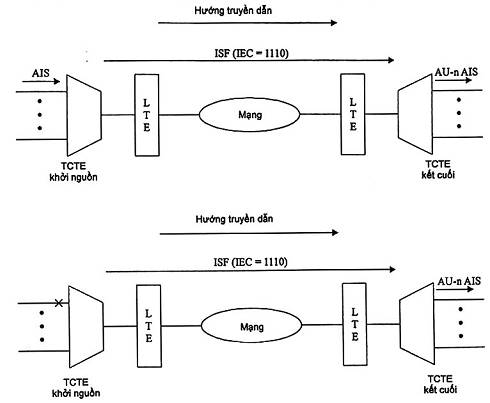

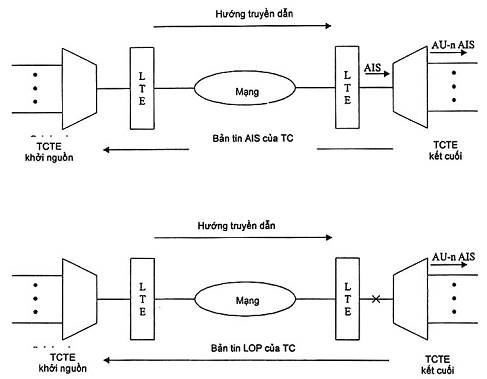

Tín hiệu chỉ thị cảnh báo (AIS) là tín hiệu được gửi theo chiều đi chỉ thị rằng có sai hỏng trong luồng tín hiệu theo chiều lên được phát hiện.

5.2.4.1.1 MS-AIS

AIS đoạn ghép kênh (MS-AIS) được quy định có giá trị là "1" trong toàn bộ khung STM-N, trừ trong phần STM-N RSOH.

5.2.4.1.2 MSF-AIS

FEC AIS đoạn ghép kênh (MSF-AIS) được quy định có giá trị là "1" trong toàn bộ khung STM-N, ngoại trừ phần STM-N RSOH không kể các byte P1 và Q1.

5.2.4.1.3 AU/TU-AIS

AIS khối quản lý (AU-AIS) được quy định có giá trị là "1" trong toàn bộ AU-n (n=3, 4, 4-Xc), kể cả trong con trỏ AU-n.

AIS khối nhánh (TU-AIS) được quy định có giá trị là "1" trong toàn bộ TU-n (n=11, 12, 2, 3), kể cả trong con trỏ TU-n.

5.2.4.1.4 VC-AIS

Tín hiệu AU/TU-AIS đến kết nối chuyển tiếp (TC) được chuyển đổi thành AIS container ảo (VC-AIS) trong kết nối chuyển tiếp vì để giám sát kết nối chuyển tiếp (TCM) cần có con trỏ AU-n/TU-n hợp lệ.

VC-n (n=3, 4, 4-Xc) AIS được quy định có giá trị là "1" trong toàn bộ VC-n khi byte nhà khai thác mạng N1 có giá trị hợp lệ, chức năng TCM được cung cấp và có mã phát hiện lỗi hợp lệ trong byte B3.

VC-m (m=11, 12, 2) AIS được quy định có giá trị là "1" trong toàn bộ VC-m khi byte khai thác mạng N2 có giá trị hợp lệ, chức năng TCM được cung cấp và có mã phát hiện lỗi hợp lệ trong các bit 1 và 2 của byte V5.

5.2.4.2 Tín hiệu thông báo luồng VC-n/VC-m không sẵn sàng

5.2.4.2.1 Trong trường hợp mạng có cung cấp truyền tải tín hiệu kết nối chuyển tiếp

Trong trường hợp mạng có cung cấp truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-n (n=3, 4) hoặc VC-4-Xc không sẵn sàng là tín hiệu có tất cả các bit là "0" trong các byte nhãn tín hiệu luồng container ảo bậc cao (C2), byte giám sát kết nối chuyển tiếp (N1) và byte truy vết luồng (J1), và có byte BIP-8 (B3) hợp lệ. Các byte trong phần tải tin của container ảo và phần còn lại của mào đầu luồng không được quy định.

Trong trường hợp mạng có cung cấp truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-m (m=11, 12, 2) không sẵn sàng là tín hiệu có tất cả các bit là "0" trong các byte nhãn tín hiệu luồng container ảo bậc thấp (bit 5, 6, 7 của byte V5), byte giám sát kết nối chuyển tiếp (N2) và byte truy vết luồng (J2), và có BIP-2 (bit 1, 2 của byte V5) hợp lệ. Các byte trong phần tải tin của container ảo và phần còn lại của mào đầu luồng không được quy định.

Các tín hiệu này chỉ cho chức năng xử lý truyền tải đường xuống biết rằng container ảo hiện đang không bị chiếm, không nối vào chức năng nguồn kết cuối luồng. Các thông tin về chất lượng chỉ được cung cấp thông qua giám sát BIP.

Trong kết nối chuyển tiếp, tín hiệu không sẵn sàng VC-n/VC-m được tạo ra trước khi các byte giám sát kết nối chuyển tiếp (N1, N2) có giá trị hợp lệ (khi mà không phải tất cả các bit của N1 và N2 đều có giá trị là "0").

5.2.4.2.2 Trường hợp mạng không hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp

Đối với trường hợp mạng không hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-n (n=3, 4) hoặc VC-4-Xc không sẵn sàng là tín hiệu có tất cả các bit là "0" trong các byte nhãn tín hiệu luồng container ảo bậc cao (C2) và byte truy vết luồng (J1), và có BIP-8 (B3) hợp lệ. Các byte trong phần tải tin của container ảo và phần còn lại của mào đầu luồng không được quy định.

Đối với trường hợp mạng không hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-m (m=11, 12, 2) không sẵn sàng là tín hiệu có tất cả các bit là "0" trong các byte nhãn tín hiệu luồng container ảo bậc thấp (bit 5, 6, 7 của byte V5) và byte truy vết luồng (J2), và có byte BIP-2 (bit 1, 2 của byte V5) hợp lệ. Các byte trong phần tải tin của container ảo và phần còn lại của mào đầu luồng là không được quy định.

5.2.4.3 Tín hiệu VC-n/VC-m không sẵn sàng, có giám sát

5.2.4.3.1 Trường hợp mạng hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp

Trong trường hợp mạng hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-n (n=3, 4) hoặc VC-4-Xc không sẵn sàng, giám sát, có giám sát là tín hiệu có tất cả các bit là "0" trong các byte nhãn tín hiệu luồng container ảo bậc cao (C2) và byte giám sát kết nối chuyển tiếp (N1), và có BIP-8 (B3), byte truy vết luồng (J1) và byte trạng thái của luồng (G1) hợp lệ. Các byte trong phần tải tin của container ảo không được quy định. Nội dung trong phần còn lại của các byte mào đầu luồng F2, H4, F3 và K3 còn đang được nghiên cứu tiếp.

Tín hiệu VC-n (n=3, 4) không sẵn sàng, có giám sát tín hiệu là VC-n không sẵn sàng nâng cao.

Trong trường hợp mạng hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-m (m=11, 12, 2) không sẵn sàng, có giám sát là tín hiệu có tất cả các bit là "0" trong các bit nhãn tín hiệu luồng conainer ảo bậc thấp (bit 5, 6, 7 của byte V5) và byte giám sát kết nối chuyển tiếp (N2), và có BIP-2 (bit 1, 2 của byte V5), byte truy vết luồng (J2) và trạng thái của luồng (bit 3 và 8 của byte V5) hợp lệ. Các byte trong phần tải tin của container ảo không được quy định. Nội dung trong phần còn lại của các byte/bit mào đầu luồng (bit 4 trong byte V5 và K3) còn đang được nghiên cứu tiếp.

Tín hiệu VC-m (m=11, 12, 2) không sẵn sàng, có giám sát là tín hiệu VC-m không sẵn sàng nâng cao.

Các tín hiệu này thông báo cho chức năng xử lý truyền tải đường xuống biển rằng container ảo hiện đang không bị chiếm và được tạo ra bởi bộ phát giám sát. Các thông tin về chất lượng, nguồn và trạng thái của kết nối được cung cấp thông tin chỉ thị lỗi bit, vết luồng và trạng thái của luồng.

Trong kết nối chuyển tiếp, tín hiệu VC-n/VC-m không sẵn sàng, có giám sát được tạo ra trước khi các byte giám sát kết nối chuyển tiếp (N1, N2) có giá trị hợp lệ (khi mà không phải tất cả các bit của N1 và N2 đều có giá trị là "0").

5.2.4.3.2 Trường hợp mạng không hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp

Trong trường hợp mạng không hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-n (n=3, 4) hoặc VC-4-Xc không sẵn sàng, có giám sát là tín hiệu có tất cả các bit là "0" trong các byte nhãn tín hiệu luồng container ảo bậc cao (C2), có BIP-8 (B3), byte nhận dạng vết luồng (J1) và byte trạng thái của luồng (G1) hợp lệ. Các byte trong phần tải tin của container ảo không được quy định. Nội dung trong phần còn lại của các byte mào đầu luồng F2, H4, F3, K3 và N1 còn đang được nghiên cứu tiếp.

Trong trường hợp mạng không hỗ trợ việc truyền tải tín hiệu kết nối chuyển tiếp, tín hiệu VC-m (m=11, 12, 2) không sẵn sàng, có giám sát là tín hiệu có tất cả các bit là "0" trong nhãn tín hiệu luồng container ảo bậc cao (bit 5, 6, 7 của byte V5), có BIP-2 (bit 1, 2 của byte V5), byte nhận dạng vết luồng (J2) và trạng thái của luồng (bit 3 và 8 của byte V5) hợp lệ. Các byte trong phần tải tin của container ảo không được quy định. Nội dung trong phần còn lại của các byte/bit mào đầu luồng (bit 4 trong V5, N2 và K4) còn đang được nghiên cứu tiếp.

5.3 Phân cấp tốc độ

Tốc độ bit của phân cấp SDH được quy định trên Bảng 2.

Bảng 2 - Tốc độ bit phân cấp SDH

| Mức phân cấp số đồng bộ | Tốc độ bit phân cấp (kbit/s) |

| 0 | 51 840 |

| 1 | 155 520 |

| 4 | 622 080 |

| 16 | 2 488 320 |

| 64 | 9 953 280 |

| 256 | 39 813 120 |

| CHÚ THÍCH - Chỉ tiêu kỹ thuật của các tốc độ phân cấp cao hơn 256 đang được tiếp tục nghiên cứu. | |

5.4 Kết nối các tín hiệu STM-N

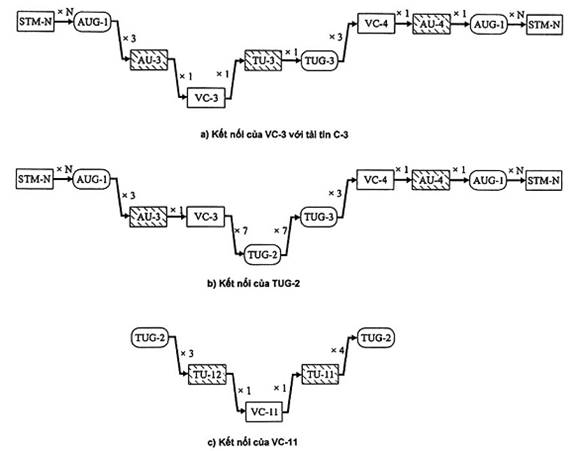

SDH được thiết kế để truyền tải nhiều loại tín hiệu khác nhau, bao gồm tất cả các tín hiệu được quy định trong khuyến nghị ITU-T G.702. Khi truyền tải các container ảo có các cấu trúc khác nhau, các qui tắc kết nối sau sẽ được sử dụng:

a) Kết nối hai AUG-1 có cấu trúc từ hai loại AU khác nhau là AU-4 và AU-3 sẽ sử dụng các trúc AU-4. AUG-1 có cấu trúc từ AU-3 sẽ được tách về VC-3 hoặc TUG-2 sau đó lại được ghép lại thành AUG-1 thông qua đường ghép TUG-3/VC-4/AU-4 như trên Hình 10a và Hình 10b.

b) Kết nối các VC-11 được cấu trúc từ hai loại TU-11 và TU-12 sẽ sử dụng cấu trúc TU-11 như trên hình 10c.

c) Kết nối các VC-3s/4s liên kết được truyền tải trên các kiểu liên kết khác nhau (liên kết liên tục và liên kết ảo) sẽ sử dụng kết chuỗi liền kề (trừ khi có sự thỏa thuận khác giữa các nhà cung cấp dịch vụ truyền tải)

Hình 10 - Kết nối các STM-N

5.5 Trộn tín hiệu

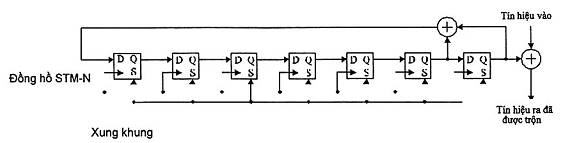

Tín hiệu STM-N (N=0, 1, 4, 16, 64 và 256) phải được trộn theo đa thức 1 + X6 + X7 theo sơ đồ trên Hình 11 dưới đây. Việc trộn tín hiệu được thực hiện cho tất cả các byte của khung SDH trừ hàng đầu tiên của byte quản lý STM-N SOH. Bộ trộn được đặt về "1111111" ngay sau byte cuối cùng của hàng đầu tiên của byte quản lý SOH.

Với các byte nằm trong hàng đầu tiên của STM-256 SOH, chỉ có các byte nằm ở các vị trí S (1,3,193) [1,705] to S (1,4,64) [1,832] là không được trộn. Bộ trộn vẫn làm việc ở các vị trí khung này nên đối với STM-256, các byte SOH ở vị trí từ S (1,1,1) [1,1] đến S (1,3,192) [1,704] và từ S (1,4,65) [1,833] đến (1,9,256) [1,2304] phải được trộn với bộ trộn được thiết lập lại ở khung STM-256 trước đó.

Hình 11 - Sơ đồ chức năng của bộ trộn đồng bộ khung

CHÚ THÍCH 1 - Để tránh không có một chuỗi dài các bit "1" hoặc "0" xuất hiện, cần phải lưu ý khi lựa chọn nội dung của byte Z0 và các byte được dành cho quốc gia vì các byte này không tham gia vào quá trình trộn

Đối với hàng đầu tiên của các byte SOH của STM-256, thì chỉ có S (1,3,193) [1,705] đến S (1,4,64) [1,832] sẽ không bị trộn.

CHÚ THÍCH 2 - Bộ trộn tiếp tục hoạt động ở các vị trí khung nêu trên

CHÚ THÍCH 3 - Do vậy, đối với STM-256, các byte SOH S (1,1,1) [1,1] đến S (1,3,192) [1,704] và S (1,4,65) [1,833] đến S (1,9,256) [1,2304] sẽ được trộn bằng bộ trộn chạy từ vị trí reset ở khung STM-256 đầu tiên.

CHÚ THÍCH 4 - Đối với các byte không sử dụng nằm trong hàng 1 của khung STM-256, phải chọn mẫu bit sao cho có đủ chuyển tiếp tín hiệu và không có sự mất cân bằng đáng kể về DC sau khi thực hiện trộn.

5.6 Giao diện vật lý của NNI

Chỉ tiêu về đặc tính giao diện điện của NNI được quy định trong ITU-T G.703. Chỉ tiêu về đặc tính giao diện quang NNI được quy định trong ITU-T G.957 và G.691.

6. Yêu cầu kỹ thuật cho phương pháp ghép kênh

6.1 Ghép kênh khối quản lý vào STM-N

6.1.1 Ghép các nhóm khối quản lý (AUG) vào STM-N

6.1.1.1 Ghép các AUG-N và STM-N, N=(1, 4, 16, 64, 256)

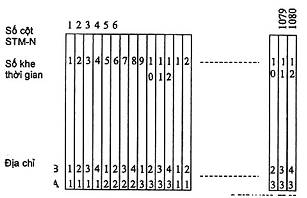

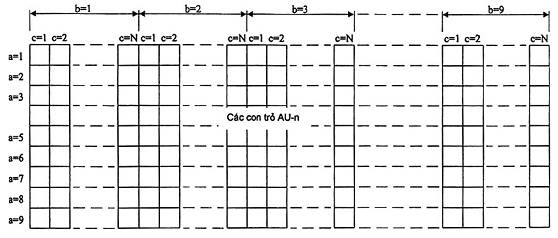

AUG-N được quy định có cấu trúc gồm 9 hàng, N x 261 cột và thêm N x 9 byte ở hàng 4 (các byte này dành cho con trỏ AU-n). STM-N bao gồm SOH và cấu trúc 9 hàng, N x 261 cột và N x 9 byte ở hàng 4 (dành cho con trỏ AU-n). AUG-N được ghép kênh vào cấu trúc này và có pha cố định so với STM-N (xem Hình 12)

Hình 12 - Ghép kênh AUG-N vào STM-N

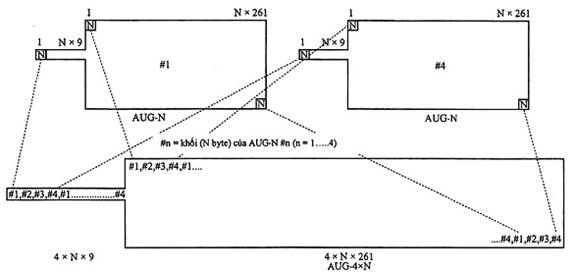

6.1.1.2 Ghép kênh các AUG-N vào AUG-4xN

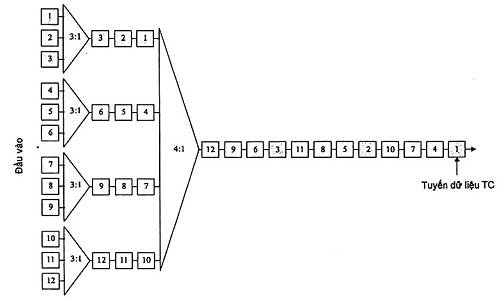

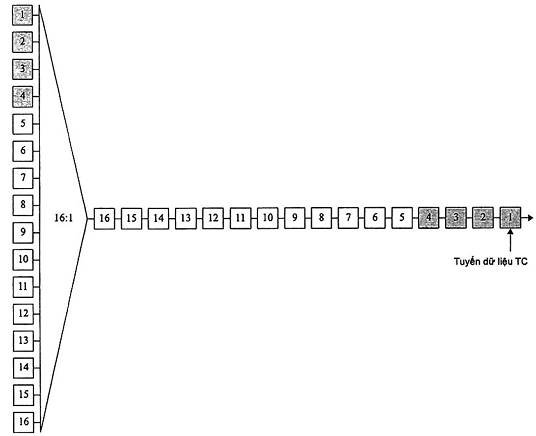

Phương pháp ghép 4 AUG-N vào AUG-4xN được quy định trên Hình 13. 4 AUG-N được ghép xen kẽ theo khối, mỗi khối gồm N byte để tạo thành cấu trúc AUG-4xN. Các AUG-N có pha cố định so với AUG-4xN

Hình 13 - Ghép kênh 4 AUG-N vào AUG-4xN

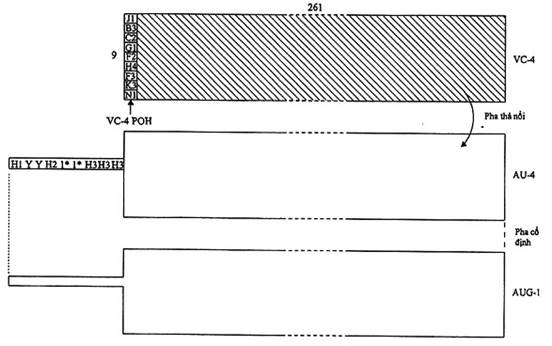

6.1.2 Ghép kênh AU-4 thành AUG-1

Phương pháp ghép kênh AU-4 vào AUG-1 được quy định trên Hình 14. 9 byte đầu tiên của hàng 4 được dành cho con trỏ AU-4, 9 hàng, 261 cột còn lại sẽ được dành cho container ảo VC-4. Pha của VC-4 không cố định so với AU-4. Vị trí byte đầu tiên của VC-4 được xác định bởi con trỏ AU-4, AU-4 được đặt trực tiếp vào trong AUG-1.

1* Tất cả các byte là 1

Y 1001 SS11 (các bit S chưa xác định)

Hình 14 - Ghép kênh các AU-4 thành AUG-1

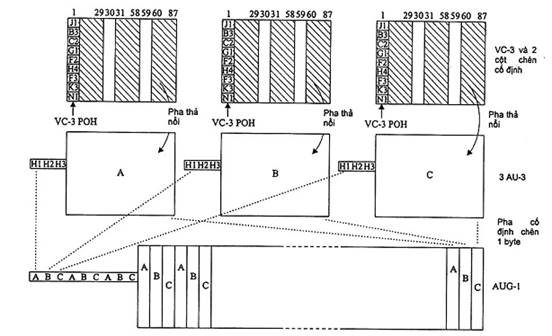

6.1.3 Ghép kênh các AU-3 thành AUG-1

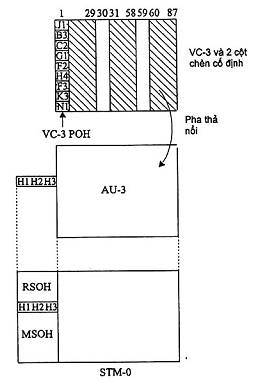

Phương pháp ghép kênh 3 AU-4 thành AUG-1 được quy định trên Hình 15. Ba byte đầu tiên của hàng 4 được dành cho con trỏ AU-3. 9 hàng, 87 cột còn lại được dành cho VC-3 và hai cột các byte chèn cố định. Các byte ở mỗi hàng trong hai cột chèn cố định của các AU-3 là như nhau. Pha của VC-3 và hai cột chèn cố định là không cố định so với AU-3. Vị trí byte đầu tiên của VC-3 được xác định bởi giá trị của con trỏ AU-3. Các AU-3 được ghép theo từng byte trong cấu trúc AUG-1.

CHÚ THÍCH - Các byte trong mỗi hàng của 2 cột chèn cố định của mỗi AU-3 là giống nhau

Hình 15 - Ghép kênh các AU-3 thành cấu trúc AUG-1

6.1.4 Ghép kênh AU-3 vào STM-0

AU-3 được cấu trúc gồm có 9 hàng 87 cột và cộng thêm 3 byte ở hàng 4 (3 byte này được dành cho con trỏ AU-3). Khung STM-0 bao gồm phần SOH và có cấu trúc 9 hàng 87 cột cộng thêm 3 byte ở hàng 4 (dành cho con trỏ AU-3). AU-3 được ghép kênh vào cấu trúc này và có pha cố định so với STM-0 như minh họa trên Hình 16.

CHÚ THÍCH - Các byte trong mỗi hàng của 2 cột chèn cố định của mỗi AU-3 là giống nhau

Hình 16 - Ghép kênh AU-3 vào STM-0

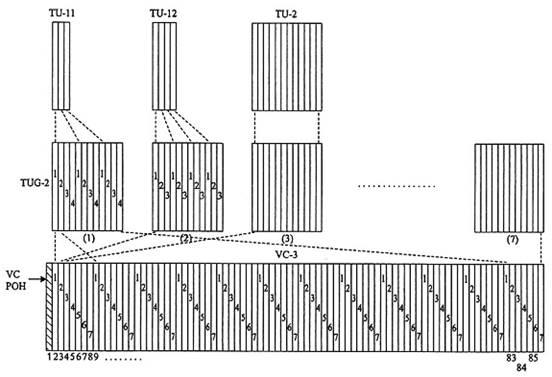

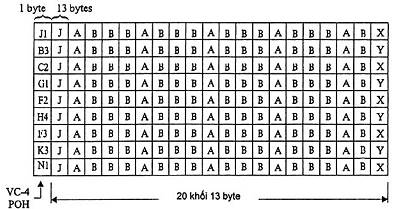

6.2 Ghép kênh các khối nhánh vào VC-4 và VC-3

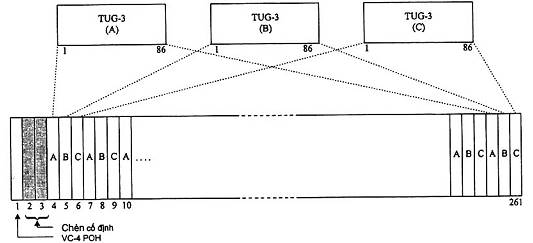

6.2.1 Ghép kênh các TUG-3 vào VC-4

Quá trình ghép 3 TUG-3 vào trong VC-4 được quy định trên Hình 17. TUG-3 có cấu trúc 9 hàng 86 cột. VC-4 gồm có một cột của VC-4 POH, hai cột chèn cố định và 258 cột dành cho phần tải tin. Ba TUG-3 được ghép theo byte vào cấu trúc tải tin có 9 hàng 258 cột của VC-4 và có pha cố định so với VC-4. Pha của VC-4 so với AU-4 được chỉ ra bởi con trỏ AU-4

Hình 17 - Ghép kênh 3 TUG-3 vào VC-4

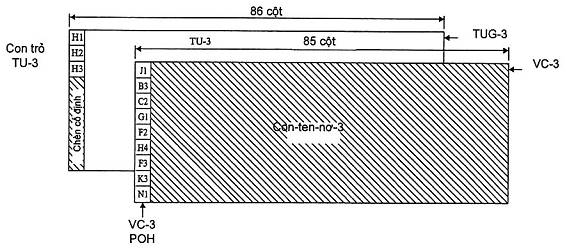

6.2.2 Ghép kênh TU-3 thành cấu trúc TUG-3

Việc ghép kênh TU-3 thành cấu trúc TUG-3 được quy định trên Hình 18. TU-3 gồm có VC-3, 9 byte VC-3 POH và con trỏ TU-3. Cột đầu tiên trong cấu trúc 9 hàng 86 cột của TUG-3 được dành cho con trỏ TU-3 (các byte H1, H2, H3) và các byte chèn cố định. Pha của VC-3 so với TUG-3 được xác định bởi con trỏ TU-3.

Hình 18 - Ghép kênh TU-3 thành cấu trúc TUG-3

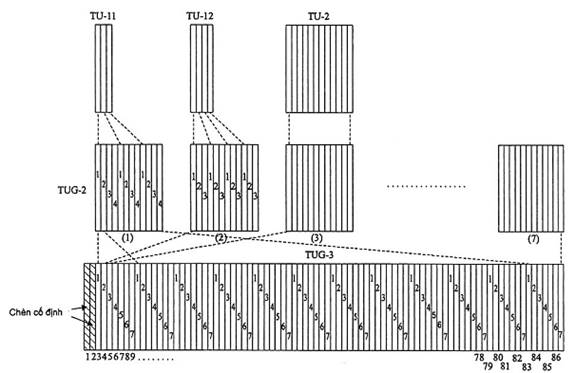

6.2.3 Ghép kênh các TUG-2 thành TUG-3

Phương pháp ghép kênh các TUG-2 thành cấu trúc TUG-3 được quy định trên Hình 19. TUG-3 có cấu trúc 9 hàng 86 cột với hai cột đầu tiên là các byte chèn cố định.

Hình 19 - Ghép kênh bảy TUG-2 thành cấu trúc TUG-3

Nhóm gồm 7 TUG-2 có thể ghép thành cấu trúc TUG-3 (như minh họa trên Hình 20). Các TUG-2 được ghép xen kẽ theo từng byte trong cấu trúc TUG-3.

Hình 20 - Ghép kênh 7 TUG-2 thành cấu trúc TUG-3

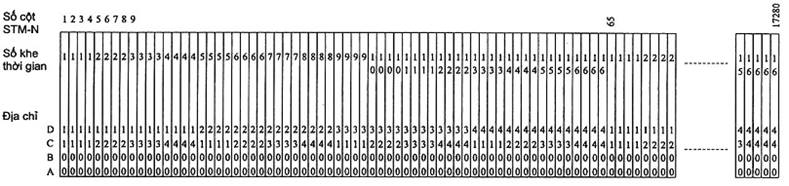

6.2.4 Ghép kênh các TUG-2 vào khung VC-3

Phương pháp ghép kênh các TUG-2s vào VC-3 được quy định trên Hình 21. VC-3 gồm có VC-3 POH và phần tải tin có cấu trúc 9 hàng 84 cột. 7 TUG-2 sẽ được ghép kênh vào trong VC-3 bằng cách ghép xen kẽ từng byte như minh họa trên Hình 22. Từng TUG-2 sẽ có vị trí cố định trong khung VC-3.

Hình 21- Ghép kênh 7 TUG-2 vào khung VC-3

(BỔ SUNG THÊM HÌNH)

Hình 22- Ánh xạ bảy TUG-2 thành một VC-3

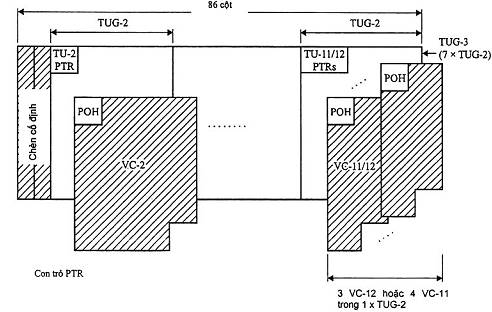

6.2.5 Ghép kênh TU-2 thành TUG-2

Phương pháp ghép TU-2 thành TUG-2 được quy định trên Hình 22.

6.2.6 Ghép kênh TU-11 hoặc TU-12 thành TUG-2

Phương pháp ghép kênh 4 TU-11 hoặc 3 TU-12 thành TUG-2 được quy định trên Hình 22. Các TU-11/TU-12 được ghép xen kẽ theo từng byte trong khung TUG-2.

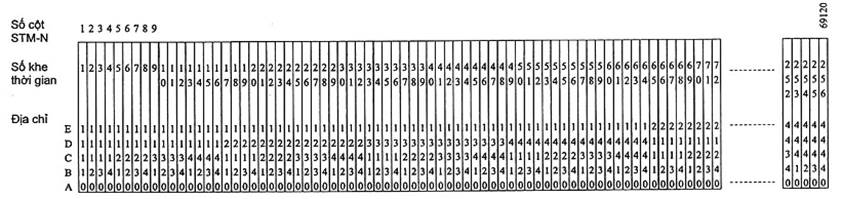

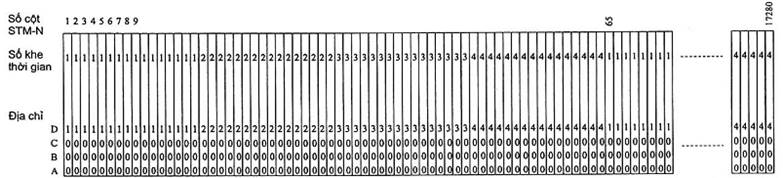

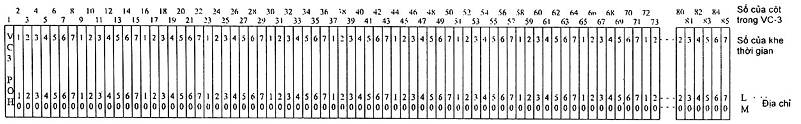

6.3 Đánh số AU-n/TU-n

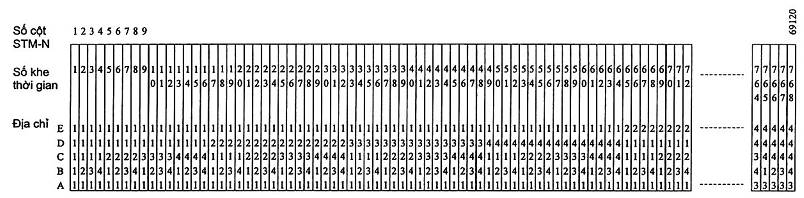

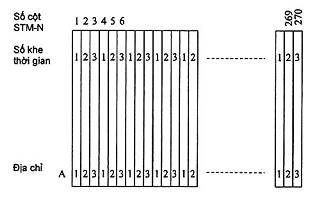

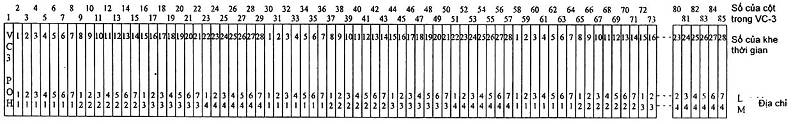

Khung STM-N gồm N x 270 cột (đánh số từ 1 đến N x 270). N x 9 cột đầu tiên chứa SOH và con trỏ AU-4/AU-4-Xc. N x 261 cột còn lại chứa tải tin bậc cao (các nhánh bậc cao).

Các cột tải tin bật cao có thể được đánh địa chỉ bằng hai tham số (B,A) hoặc ba tham số (C,B,A) hoặc bốn tham số (D,C,B,A) hoặc năm tham số (E,D,C,B,A). Trong đó: A là số của AU-3, B là số của AUG-1, C là số của AUG-4, D là số của AUG-16 và E là số của AUG-64. (Xem từ Hình 28 đến Hình 36)

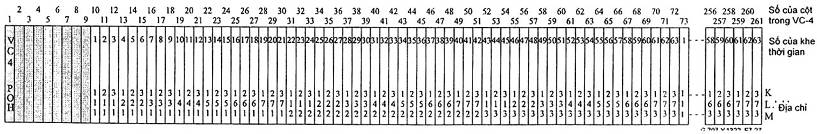

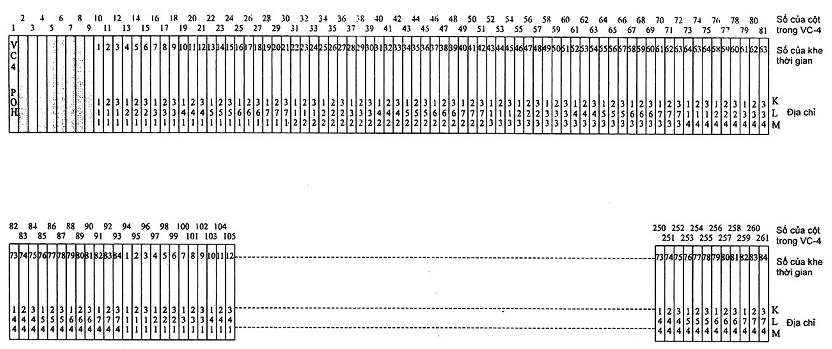

Trong trường hợp khung có cấu trúc AU-4, các cột tải tin có thể được đánh số bằng ba tham số địa chỉ (K, L, M), trong đó K là số của TUG-3, L là số của TUG-2 và M là số của TU-11/TU-12 (xem trong các Hình 38, Hình 39 và Bảng 3). Trong trường hợp khung có cấu trúc AU-3, chỉ sử dụng hai tham số là L và M (xem Hình 42 và Bảng 4).

Để đơn giản trong việc xác định tổng dung lượng nhánh, tức là số các nhánh bậc thấp được cung cấp, các cột của tải tin phân một số khe thời gian. Số khe thời gian dành cho mỗi nhánh trong mỗi khung được xác định bởi cấu hình của tải tin.

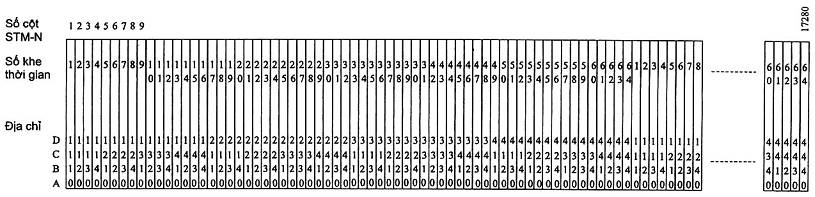

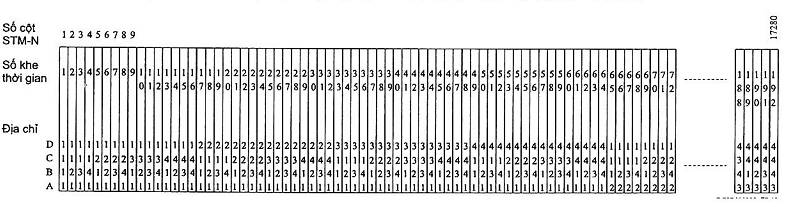

Khe thời gian (TS) AU được đánh số từ trái sang phải trong khung STM-N như minh họa trên các hình từ Hình 28 đến Hình 37. Khe thời gian (TS) TU được đánh số từ trái sang phải trong khung VC-4/VC-3 như minh họa trên các hình từ Hình 38 đến Hình 40.

AU và TU cũng có thể được đánh số hoặc theo phân cấp tuần tự (như minh họa trên các hình từ Hình 28 đến Hình 40 bằng số của khe thời gian hoặc bằng cách sử dụng phân cấp ghép kênh (như minh họa trên hình từ Hình 28 đến Hình 40 bằng địa chỉ.

6.3.1 Đánh số các AU-n (VC-n) trong khung STM-2576

STM-256 có thể bao gồm 4 AUG-64s, được đánh số từ #1 đến #4:

- AUG-64 #1 nằm ở các cột 1…64, 257…320, 513…576,…, của khung STM-256;

- AUG-64 #2 nằm ở các cột 65…128, 321…384, 577…640,… của khung STM-256;

- AUG-64 #3 nằm ở các cột 129…192, 385…448, 641…704,… của khung STM-256;

- AUG-64 #4 nằm ở các cột 193…256, 449…512, 705…768,… của khung STM-256.

Mỗi AUG-64 có thể bao gồm bốn AUG-16, được đánh số từ #1 đến #4. Mỗi AUG-16 có thể bao gồm bốn AUG-4, được đánh số từ #1 đến #4. Mỗi AUG-4 có thể bao gồm bốn AUG-1, được đánh số từ #1 đến #4. Mỗi AUG-1 có thể bao gồm ba AU-3s, được đánh số từ #1 đến #3.

6.3.1.1 Đánh số các AU-4s (VC-4s) trong khung STM-256

AU-4 được đánh số ở dạng #E, #D, #C, #B, #A, trong đó E là số của AUG-64 (được đánh số từ 1 đến 4), D là số của AUG-16 (được đánh số từ 1 đến 4), C là số của AUG-4 (được đánh số từ 1 đến 4), B là số của AUG-1 (được đánh số từ 1 đến 4), và A luôn bằng 0 (xem Hình 23). Vị trí của AU-4 (E,D,C,B,0) trong khung STM-256 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = 1 + 64 x [E - 1] + 16 x [D - 1] + 4 x [C - 1] + [B - 1] + 256 x [X - 1] với X = 1 đến 270.

Hình 23 - Đánh số AU-4 trong khung STM-256

6.3.1.2 Đánh số AU-3 (VC-3) trong khung STM-256

AU-3 được đánh số ở dạng #E, #D, #C, #B, #A, trong đó E là số của AUG-64 (được đánh số từ 1 đến 4), D là số của AUG-16 (được đánh số từ 1 đến 4), C là số của AUG-4 (được đánh số từ 1 đến 4), B là số của AUG-1 (được đánh số từ 1 đến 4), và A là số của AU-3 (được đánh số từ 1 đến 3). (xem Hình 24). Vị trí của AU-3 (E,D,C,B,A) trong khung STM-256 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = 1 + 64 x [E - 1] + 16 x [D - 1] + 4 x [C - 1] + [B - 1] + 256 x [A - 1] + 768 x [X - 1] với X = 1 đến 90.

Hình 24 - Đánh số AU-3 trong khung STM-256

6.3.1.3 Đánh số AU-4-4c (VC-4-4c) trong khung STM-256

AU-4-4c được đánh số ở dạng #E, #D, #C, #B, #A, trong đó E là số của AUG-64 (được đánh số từ 1 đến 4), D là số của AUG-16 (được đánh số từ 1 đến 4), C là số của AUG-4 (được đánh số từ 1 đến 4), B và A luôn có giá trị là 0. (xem Hình 25). Vị trí của AU-4-4c (E,D,C,0,0) trong khung STM-256 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = [X mod 4] + 64 x [E - 1] + 16 x [D - 1] + 4 x [C - 1] + 256 x [X DIV 4] với X = 1 đến 1080.

Hình 25 - Đánh số AU-4-4c trong khung STM-256

6.3.1.4 Đánh số AU-4-16c (VC-4-16c) trong khung STM-256

AU-4-16c được đánh số ở dạng #E, #D, #C, #B, #A, trong đó E là số của AUG-64 (được đánh số từ 1 đến 4), D là số của AUG-16 (được đánh số từ 1 đến 4), C, B và A luôn có giá trị là 0. (xem Hình 26). Vị trí của AU-4-16c (E,D,0,0,0) trong khung STM-256 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = [X mod 16] + 64 x [E - 1] + 16 x [D - 1] + 256 x [X DIV 16] với X = 1 đến 4320.

Hình 26 - Đánh số AU-4-16c trong khung STM-256

6.3.1.5 Đánh số AU-4-64c (VC-4-64c) trong khung STM-256

AU-4-16c được đánh số ở dạng #E, #D, #C, #B, #A, trong đó E là số của AUG-64 (được đánh số từ 1 đến 4), D, C, B và A luôn có giá trị là 0. (xem Hình 27). Vị trí của AU-4-64c (E,0,0,0,0) trong khung STM-256 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = [X mod 64] + 64 x [E - 1] + 256 x [X DIV 64] với X = 1 đến 17 280.

Hình 27 - Đánh số AU-4-64c trong khung STM-256

6.3.1.6 Đánh số AU-4-256c trong khung STM-256

Trong khung STM-256 chỉ có thể chứa được một AU-4-256c. Tín hiệu này không cần đánh số nhưng cũng có thể coi là có số (0, 0, 0, 0, 0)

6.3.2 Đánh số AU-n (VC-n) trong khung STM-64

STM-64 có thể bao gồm 4 AUG-16, được đánh số từ #1 đến #4:

- AUG-16 #1 nằm ở các cột 1…16, 65…80, 129…144… của khung STM-64;

- AUG-16 #2 nằm ở các cột 17…32, 81…96, 145…160… của khung STM-64;

- AUG-16 #3 nằm ở các cột 33…48, 97…112, 161…176,… của khung STM-64;

- AUG-16 #4 nằm ở các cột 49…64, 113…128, 177…192 của khung STM-64.

Mỗi AUG-16 có thể bao gồm 4 AUG-4, được đánh số từ #1 đến #4. Mỗi AUG-4 có thể bao gồm 4 AUG-1, được đánh số từ #1 đến #4. Mỗi AUG-1 có thể bao gồm 4 AU-3s, được đánh số từ #1 đến #3.

6.3.2.1 Đánh số các AU-4 (VC-4) trong khung STM-64

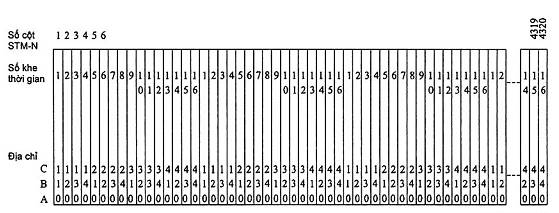

AU-4 được đánh số ở dạng #D, #C, #B, #A, trong đó D là số của AUG-16 (được đánh số từ 1 đến 4), C là số của AUG-4 (được đánh số từ 1 đến 4), B là số của AUG-1 (được đánh số từ 1 đến 4), và A luôn bằng 0 (xem Hình 28). Vị trí của AU-4 (D,C,B,0) trong khung STM-64 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = 1 + 16 X [D - 1] + 4 x [C - 1] + [B - 1] + 64 x [X - 1] với X = 1 đến 270.

Hình 28 - Đánh số AU-4 trong khung STM-64

6.3.2.2 Đánh số các AU-3 (VC-3) trong khung STM-64

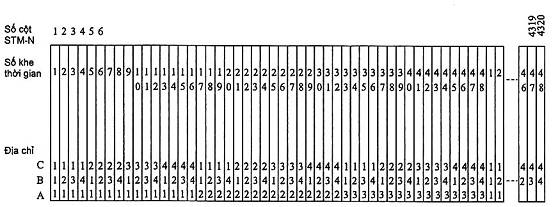

AU-3 được đánh số ở dạng #D, #C, #B, #A, trong đó D là số của AUG-16 (được đánh số từ 1 đến 4), C là số của AUG-4 (được đánh số từ 1 đến 4), B là số của AUG-1 (được đánh số từ 1 đến 4), và A là số của AU-3 (được đánh số từ 1 đến 3). (xem Hình 29). Vị trí của AU-3 (D,C,B,A) trong khung STM-64 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = 1 + 16 X [D - 1] + 4 x [C - 1] + [B - 1] + 64 x [A - 1] + 192 x [X - 1] với X = 1 đến 90.

Hình 29 - Đánh số AU-3 trong khung STM-64

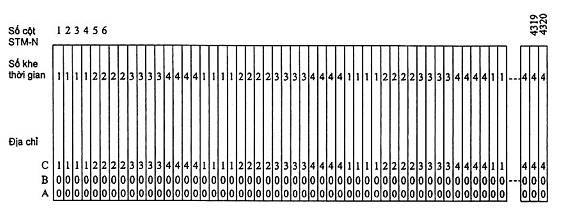

6.3.2.3 Đánh số các AU-4-4c (VC-4-4c) trong khung STM-64

AU-4-4c được đánh số ở dạng #D, #C, #B, #A, trong đó D là số của AUG-16 (được đánh số từ 1 đến 4), C là số của AUG-4 (được đánh số từ 1 đến 4), B và A luôn có giá trị là 0 (xem Hình 30). Vị trí của AU-4-4c (D,C,0,0) trong khung STM-64 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = [X mod 4] + 16 X [D - 1] + 4 x [C - 1] + 64 x [X DIV 4] với X = 1 đến 1080.

Hình 30 - Đánh số AU-4-4c trong khung STM-64

6.3.2.4 Đánh số các AU-4-16c (VC-4-16c) trong khung STM-64

AU-4-16c được đánh số ở dạng #D, #C, #B, #A, trong đó D là số của AUG-16 (được đánh số từ 1 đến 4), C, B và A luôn có giá trị là 0 (xem Hình 31). Vị trí của AU-4-16c (D,0,0,0) trong khung STM-64 sẽ nằm ở vị trí các cột được xác định như sau:

Cột thứ X = [X mod 16] + 16 X [D - 1] + 64 x [X DIV 16] với X = 1 đến 4320.

Hình 31 - Đánh số AU-4-16c trong khung STM-64

6.3.3 Đánh số AU-4-64c trong khung STM-64

Trong khung STM-64 chỉ có thể chứa được một AU-4-64c. Tín hiệu này không cần đánh số nhưng cũng có thể coi là có số (0, 0, 0, 0)

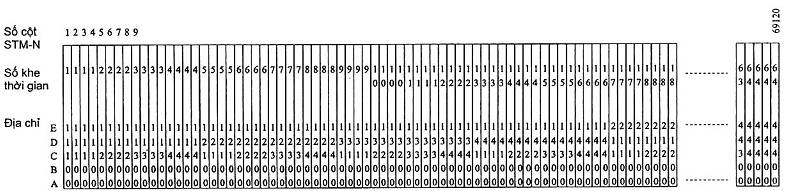

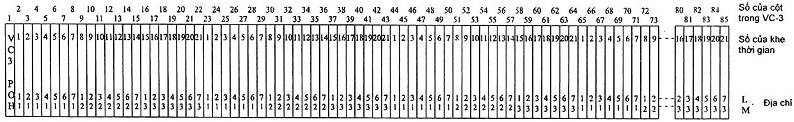

6.3.4 Đánh số AU-n (VC-n) trong khung STM-16

STM-16 có thể bao gồm 4 AUG-4, được đánh số từ #1 đến #4:

- AUG-4#1 nằm ở các cột 1…4, 17…20, 33…36,… của khung STM-16;

- AUG-4#2 nằm ở các cột 5…8, 21…24, 36…40,… của khung STM-16;

- AUG-4#3 nằm ở các cột 9…12, 25…28, 41…44,… của khung STM-16;

- AUG-4#4 nằm ở các cột 13…16, 29…32, 45…48,… của khung STM-16.

Mỗi AUG-4 có thể bao gồm 4 AUG-1, được đánh số từ #1 đến #4. Mỗi AUG-1 có thể bao gồm 3 AU-3, được đánh số từ #1 đến #3.

6.3.4.1 Đánh số AU-4 (VC-4) trong khung STM-16

AU-4 được đánh số ở dạng #C, #B, #A, trong đó C là số của AUG-4 (được đánh số từ 1 đến 4), B là số của AUG-1 (được đánh số từ 1 đến 4), và A luôn bằng 0. (xem Hình 32). Vị trí của AU-4 (C,B,0) trong khung STM-16 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 1 + 4 x [C - 1] + [B - 1] + 16 x [X - 1] với X = 1 đến 270.

Hình 32 - Đánh số AU-4 trong khung STM-16

6.3.4.2 Đánh số AU-3 (VC-3) trong khung STM-16

AU-3 được đánh số ở dạng #C, #B, #A, trong đó C là số của AUG-4 (được đánh số từ 1 đến 4), B là số của AUG-1 (được đánh số từ 1 đến 4), và A là số của AU-3 (được đánh số từ 1 đến 3). (xem Hình 33). Vị trí của AU-3 (C,B,A) trong khung STM-16 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 1 + 4 x [C - 1] + [B - 1] + 16 x [A - 1] + 48 x [X - 1] với X = 1 đến 90.

Hình 33 - Đánh số AU-3 trong khung STM-16

6.3.4.3 Đánh số AU-4-4c 4(VC-4-4c) trong khung STM-16

AU-4-4c được đánh số ở dạng #C, #B, #A, trong đó C là số của AUG-4 (được đánh số từ 1 đến 4), B, và A luôn bằng 0. (xem Hình 34). Vị trí của AU-4-4c (C,0,0) trong khung STM-16 sẽ nằm ở các cột được xác định như sau:

Cột thứ 4X-3 = 1 + [C - 1] + 16 x [X - 1] với X = 1 đến 270.

Cột thứ 4X-2 = 2 + [C - 1] + 16 x [X - 1] với X = 1 đến 270.

Cột thứ 4X-1 = 3 + [C - 1] + 16 x [X - 1] với X = 1 đến 270.

Cột thứ 4X = 4 + [C - 1] + 16 x [X - 1] với X = 1 đến 270.

Hình 34 - Đánh số AU-4-4c trong khung STM-16

6.3.4.4 Đánh số AU-4-16 trong khung STM-16

Trong khung STM-16 chỉ có thể chứa được một AU-4-16c. Tín hiệu này không cần đánh số nhưng cũng có thể coi là có số (0, 0, 0)

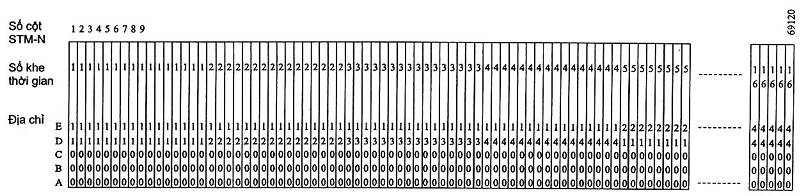

6.3.5 Đánh số AU-n (VC-n) trong khung STM-4

STM-4 có thể bao gồm 4 AUG-1, được đánh số từ #1 đến #4:

- AUG-1#1 nằm ở các cột 1, 5, 9, … của khung STM-4;

- AUG-1#2 nằm ở các cột 2, 6, 10, … của khung STM-4;

- AUG-1#3 nằm ở các cột 3, 7, 11, … của khung STM-4;

- AUG-1#4 nằm ở các cột 4, 8, 12, … của khung STM-4.

Mỗi AUG-1 có thể bao gồm ba AU-3, được đánh số từ #1 đến #3.

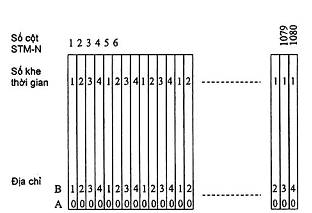

6.3.5.1 Đánh số AU-4 (VC-4) trong khung STM-4

AU-4 được đánh số ở dạng #B, #A, trong đó B là số của AUG-1 (được đánh số từ 1 đến 4), và A luôn bằng 0 (xem Hình 35). Vị trí của AU-4 (B,0) trong khung STM-4 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 1 + [B - 1] + 4 x [X - 1] với X = 1 đến 270.

Vì vậy, AU-4 (1,0) sẽ nằm ở các cột 1, 5, 9, …, 1077 của khung STM-4 và AU-4 (4,0) sẽ nằm ở các cột số 4, 8, 12,…, 1080 của khung STM-4.

Hình 35 - Đánh số AU-4 trong khung STM-4

6.3.5.2 Đánh số AU-3 (VC-3) trong khung STM-4

AU-3 được đánh số ở dạng #B, #A, trong đó B là số của AUG-1 (được đánh số từ 1 đến 4), và A là số của AU-3 (được đánh số từ 1 đến 3) (xem Hình 36). Vị trí của AU-3 (B,A) trong khung STM-4 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 1 + [B - 1] + 4 x [A - 1] + 12 x [X - 1] với X = 1 đến 90.

Hình 36 - Đánh số AU-3 trong khung STM-4

6.3.5.3 Đánh số AU-4-4c trong khung STM-4

Trong khung STM-4 chỉ có thể chứa được một AU-4-4c. Tín hiệu này không cần đánh số nhưng cũng có thể coi là có số (0,0)

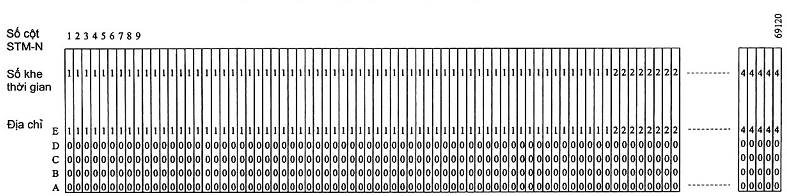

6.3.6 Đánh số AU-n (VC-n) trong khung STM-1

6.3.6.1 Đánh số AU-4 (VC-4) trong khung STM-1

Trong khung STM-1 chỉ có thể chứa được một AU-4 (VC-4). Tín hiệu này không cần đánh số nhưng cũng có thể coi là có số (0)

6.3.6.2 Đánh số AU-3 (VC-3) trong khung tín hiệu STM-1

AU-3 được đánh số ở dạng #A, trong đó A là số của AU-3 (được đánh số từ 1 đến 3) (xem Hình 37). Vị trí của AU-3 (A) trong khung STM-4 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 1 + [A - 1] + 3 x [X - 1] với X = 1 đến 90.

Hình 37 - Đánh số AU-3 trong khung STM-1

6.3.7 Đánh số AU-3 (VC-3) trong khung STM-0

Trong khung STM-0 chỉ có thể chứa được một AU-3 (VC-3). Tín hiệu này không cần đánh số nhưng cũng có thể coi là có số (0)

6.3.8 Đánh số TU-3 trong khung VC-4

Mỗi VC-4 có thể bao gồm 3 TUG-3, được đánh số từ #1 đến #3:

- TUG-3#1 (tương ứng với TUG-3 (A) trong Hình 17) nằm ở các cột 7, 10,…, 259 của khung VC-4;

- TUG-3#2 (tương ứng với TUG-3 (B) trong Hình 17) nằm ở các cột 5, 8, 11,…, 260 của khung VC-4;

- TUG-3#3 (tương ứng với TUG-3 (B) trong Hình 17) nằm ở các cột 6, 9, 12,…, 261 của khung VC-4;

Mỗi TUG-3 có thể bao gồm một TU-3. TU-3 được đánh số ở dạng #K, #L, #M, trong đó K là số của TUG-3 (được đánh số từ 1 đến 3), L và M luôn bằng 0. Vị trí của TU-3 (K,0,0) trong khung VC-4 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 4 + [K - 1] + 3 x [X - 1] với X =1 đến 86.

6.3.9 Đánh số TU-2 trong khung VC-4

Mỗi TUG-3 có thể bao gồm 7 TUG-2, được đánh số từ #1 đến #7 và mỗi TUG-2 sẽ có 1 TU-2. TU-2 được đánh số ở dạng #K, #L, #M, trong đó K là số của TUG-3 (được đánh số từ 1 đến 3), L là số của TUG-2 (được đánh số từ 1 đến 7) và M luôn bằng 0. Vị trí của TU-2 (K, L, 0) trong khung VC-4 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 10 [K - 1] + 3 x [L - 1] 21 x [X - 1] với X = 1 đến 12

6.3.10 Đánh số TU-12 trong khung VC-4

Mỗi TUG-3 có thể bao gồm 7 TUG-2, được đánh số từ #1 đến #7 và mỗi TUG-2 sẽ có 3 TU-12 được đánh số từ #1 đến #3.

TU-12 được đánh số ở dạng #K, #L, #M, trong đó K là số của TUG-3 (được đánh số từ 1 đến 3), L là số của TUG-2 (được đánh số từ 1 đến 7) và M là số của TU-12 (được đánh số từ 1 đến 3). Vị trí của TU-12 (K, L, M) trong khung VC-4 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 10 [K - 1] + 3 x [L - 1] 21 x [M - 1] 63 x [X - 1] với X = 1 đến 4

6.3.11 Đánh các số TU-11 trong khung VC-4

Mỗi TUG-3 có thể bao gồm 7 TUG-2, được đánh số từ #1 đến #7 và mỗi TUG-2 sẽ có 4 TU-11 được đánh số từ #1 đến #4.

TU-11 được đánh số ở dạng #K, #L, #M, trong đó K là số của TUG-3 (được đánh số từ 1 đến 3), L là số của TUG-2 (được đánh số từ 1 đến 7) và M là số của TU-11 (được đánh số từ 1 đến 4). Vị trí của TU-11 (K, L, M) trong khung VC-4 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 10 [K - 1] + 3 x [L - 1] 21 x [M - 1] 84 x [X - 1] với X = 1 đến 3

6.3.12 Đánh số TU-2 trong khung VC-3

Mỗi VC-3 có thể bao gồm 7 TUG-2, được đánh số từ #1 đến #7 và mỗi TUG-2 sẽ có 1 TU-2.

TU-2 được đánh số ở dạng #L, #M, trong đó L là số của TUG-2 (được đánh số từ 1 đến 7) và M luôn bằng 0. Vị trí của TU-2 (L, 0) trong khung VC-3 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 2 [L - 1] 7 x [X - 1] với X = 1 đến 12

6.3.13 Đánh số TU-12 trong khung VC-3

Mỗi TUG-2 có thể bao gồm 3 TU-12, được đánh số từ #1 đến #3. TU-12 được đánh số ở dạng #L, #M, trong đó L là số của TUG-2 (được đánh số từ 1 đến 7) và M là số của TU-12 (được đánh số từ 1 đến 3). Vị trí của TU-12 (L, M) trong khung VC-3 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 2 [L - 1] 7 x [M - 1] 21 x [X - 1] với X = 1 đến 4

6.3.14 Đánh các số TU-11 trong khung VC-3

Mỗi TUG-2 có thể bao gồm 4 TU-11, được đánh số từ #1 đến #3. TU-11 được đánh số ở dạng #L, #M, trong đó L là số của TUG-2 (được đánh số từ 1 đến 7) và M là số của TU-11 (được đánh số từ 1 đến 1). Vị trí của TU-11 (L, M) trong khung VC-3 sẽ nằm ở các cột được xác định như sau:

Cột thứ X = 2 [L - 1] 7 x [M - 1] 28 x [X - 1] với X = 1 đến 3

CHÚ THÍCH: Số của các khe thời gian trên Hình 36 và Hình 33 không được hiểu là số của cổng nhánh.

Sơ đồ đánh số TU-3

Sơ đồ đánh số TU-2

Sơ đồ đánh số TU-12

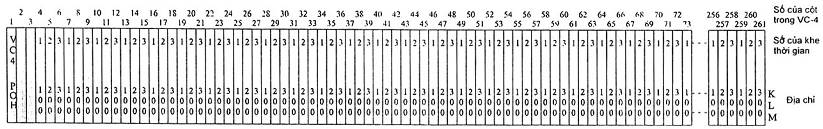

Hình 38 - Đánh số TU-3, TU-2 và TU-12 trong khung VC-4

Hình 39 - Đánh số TU-11 trong khung VC-4

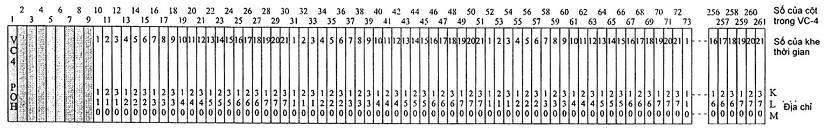

Sơ đồ đánh số TU-2

Sơ đồ đánh số TU-12

Sơ đồ đánh số TU-11

Hình 40 - Đánh số TU-2, TU-12, TU-11 trong khung VC-3

Bảng 3 - Phân bổ dung lượng của TU-n cho các khe thời gian trong khung VC-4

| Địa chỉ # |

| Địa chỉ # |

| Địa chỉ # | ||||||||||||

| TU-3 | TU-2 | TU-12 | TU-11 | TS# | TU-3 | TU-2 | TU-12 | TU-11 | TS# | TU-3 | TU-2 | TU-12 | TU-11 | TS# | ||

| 100 | 110

120

130

140

150

160

170 | 111 112 113

121 122 123

131 132 133

141 142 143

151 152 153

161 162 163

171 172 173 | 111 112 113 114 121 122 123 124 131 132 133 134 141 142 143 144 151 152 153 154 161 162 163 164 171 172 173 174 | 1 22 43 64 4 25 46 67 7 28 49 70 10 31 52 73 13 34 55 76 16 37 58 79 19 40 61 82 | 200 | 210

220

230

240

250

260

270 | 211 212 213

221 222 223

231 232 233

241 242 243

251 252 253

261 262 263

271 272 273

| 211 212 213 214 221 222 223 224 231 232 233 234 241 242 243 244 251 252 253 254 261 262 263 264 271 272 273 274 | 2 23 44 65 5 26 47 68 8 29 50 71 11 32 53 74 14 35 56 77 17 38 59 80 20 41 62 83 | 300 | 310

320

330

340

350

360

370 | 311 312 313

321 322 323

331 332 333

341 342 343

351 352 353

361 362 363

371 372 373 | 311 312 313 314 321 322 323 324 331 332 333 334 341 342 343 344 351 352 353 354 361 362 363 364 371 372 373 374 | 3 24 45 66 6 27 48 69 9 30 51 72 12 33 54 75 15 36 57 78 18 39 60 81 21 42 63 84 | ||

| Địa chỉ = TUG-3#, TUG-2#, TU-1# = #K, #L, #M | ||||||||||||||||

Bảng 4 - Phân bổ dung lượng của TU-n cho các khe thời gian trong khung VC-3

Địa chỉ #

| TU-2 | TU-12 | TU-11 | TS# |

| 10

20

30

40

50

60

70

| 11 12 13

21 22 23

31 32 33

41 42 43

51 52 53

61 62 63

71 72 73

| 11 12 13 14 21 22 23 24 31 32 33 34 41 42 43 44 51 52 53 54 61 62 63 64 71 72 73 74 | 1 8 15 22 2 9 16 23 3 10 17 24 4 11 18 25 5 12 19 26 6 13 20 27 7 14 21 28 |

| Địa chỉ = TUG-2#, TU-1# = #L, #M | |||

7. Yêu cầu kỹ thuật cho con trỏ

7.1 Con trỏ AU-n

7.1.1 Vị trí của con trỏ

Con trỏ AU-4 nằm trong các byte H1, H2, H3 như quy định trên Hình 41. Ba con trỏ AU-3 nằm trong các byte H1, H2, H3 như quy định trên Hình 42.

1* Tất cả các byte có giá trị là 1

Y 1001SS11 (các bit S không được quy định)

Hình 41 - Đánh số độ bù con trỏ AU-4

Hình 42 - Đánh số độ bù con trỏ AU-3

7.1.2 Giá trị của con trỏ AU-n

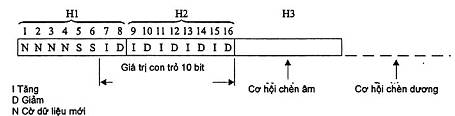

Con trỏ chứa trong H1 và H2 xác định vị trí của byte mà ở đó VC-n bắt đầu. 2 byte dành cho con trỏ được ghép thành một từ như trong Hình 43. Mười bit cuối cùng của từ con trỏ (bit 7 - 16) của từ con trỏ mang giá trị con trỏ.

Con trỏ AU-4: Giá trị của con trỏ AU-4 là một số nhị phân nằm trong dải từ 0 đến 782, giá trị này chỉ ra độ bù, tăng 3 byte, giữa con trỏ và byte đầu tiên của VC-4 (xem Hình 41)

Trong trường hợp chỉ thị liên kết, con trỏ có giá trị như sau: "1001" trong các bit từ 1 đến 4, các bit 5-6 là không xác định, các bit từ 7 đến 16 có giá trị là "1" (xem Hình 43). Con trỏ AU được thiết lập về giá trị chỉ thị liên kết trong trường hợp liên kết các AU-4 (xem 7.1.7).

Con trỏ AU-3: Giá trị con trỏ AU-3 là một số nhị phân nằm trong dải từ 0 đến 782 (xem Hình 43). Khi ghép trong khung AUG-1, mối AU-3 sẽ có các byte H1, H2 và H3 tương ứng. Các byte H được thể hiện dưới dạng kế tiếp nhau (Hình 42). Tập các byte H1, H2, H3 đầu tiên sẽ liên quan đến AU-3 đầu tiên, tập các byte H1, H2, H3 thứ hai sẽ liên quan đến AU-3 thứ hai… Đối với mỗi AU-3, các con trỏ sẽ hoạt động độc lập.

| Cờ dữ liệu mới - Cho phép khi có tối thiểu 3 trong 4 bit trùng với mẫu "1001" - Bị vô hiệu hóa khi có tối thiểu 3 trong 4 bit trùng với mẫu "0110" - Không hợp lệ với các mã khác Chèn âm - Đảo 5 D-bit - Chấp nhận các bit có ý nghĩa lớn nhất | Giá trị con trỏ (b7-b16) - Dải bình thường là: Đối với AU-4, AU-3 0-782 nhị nhân Đối với TU-3 0-764 nhị phân Chèn dương - Đảo 5 l-bit - Chấp nhận các bit có ý nghĩa lớn nhất Chỉ thị liên kết - 1001SS1111111111 (SS là các bit không được xác định) | ||

| SS 10 |

AU-4, AU-4-Xc, AU-3, TU-3 |

| |

Hình 43 - Mã hóa con trỏ AU-n/TU-3 (H1, H2, H3)

CHÚ THÍCH 1 - Các bit SS của AU-4, AU-4-Xc, AU-3 được xử lý trong thuật toán phát hiện con trỏ (xem phiên bản năm 1997 của ITU-T Rec. G.783). Từ các phiên bản 2000 của các khuyến nghị ITU-T G.783 và G.806, các bit SS không bao hàm trong thuật toán phát hiện con trỏ của AU-n.

CHÚ THÍCH 2 - Con trỏ được thiết lập tất cả về "1" khi AIS xuất hiện.

7.1.3 Hiệu chỉnh tần số

Nếu có sự lệch về tần số giữa tốc độ khung của AUG-N và VC-n, giá trị con trỏ sẽ tăng lên hoặc giảm đi tùy theo đó là chèn dương hay chèn âm. Hoạt động của con trỏ phải được phân cách nhau tối thiểu là 3 khung (tức là theo các nhóm 4 khung) trong đó giá trị của con trỏ được giữ nguyên.

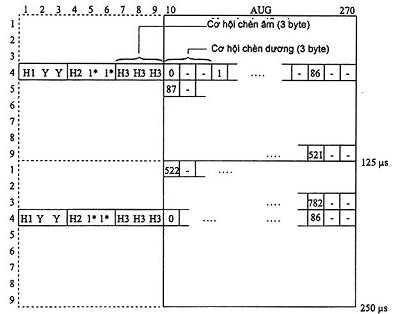

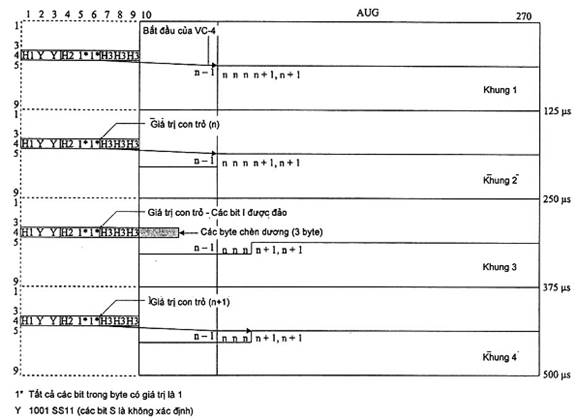

Nếu tốc độ khung của VC-n quá chậm so với AUG-n, giá trị của con trỏ phải tăng lên 1 đơn vị. Hoạt động này được chỉ thị bằng việc đảo các bit 7, 9, 11, 13 và 15 (I-bit) trong từ con trỏ để cho phép lựa chọn theo đa số của 5 bit tại bộ thu. 3 byte chèn dương xuất hiện ngay sau byte H3 cuối cùng trong khung AU-4 chứa các bit I đã được đảo. Các con trỏ tiếp theo sẽ chứa độ lệch mới. Quá trình này được minh họa trên Hình 44.

Hình 44 - Hoạt động hiệu chỉnh của con trỏ AU-4 - Chèn dương

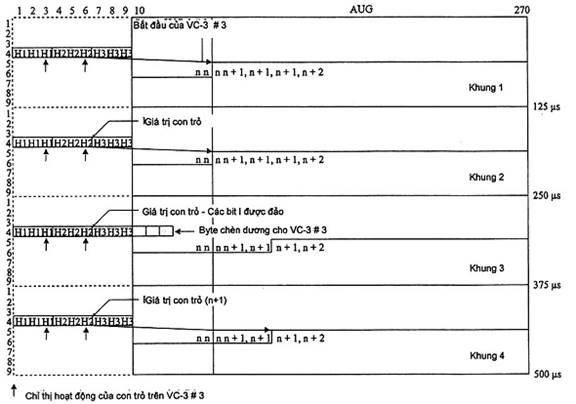

Đối với khung AU-3, byte chèn dương xuất hiện ngay sau byte H3 của khung AU-3 có chứa các bit I bị đảo. Con trỏ tiếp theo đó sẽ chứa độ lệch mới (xem minh họa trên Hình 45).

Hình 45 - Hoạt động hiệu chỉnh con trỏ AU-3 - chèn dương

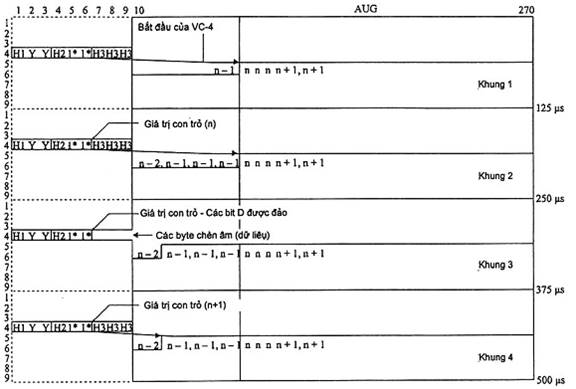

Nếu tốc độ khung của VC-n quá nhanh so với AUG-N, giá trị của con trỏ phải tăng lên 1 đơn vị. Hoạt động này được chỉ thị bằng việc đảo ngược các bit 8, 10, 12, 14 và 16 (D-bit) trong từ con trỏ để cho phép lựa chọn theo đã số của 5 bit tại bộ thu. 3 byte chèn âm xuất hiện trong byte H3 của khung AU-4 có chứa các bit D bị đảo. Con trỏ tiếp theo sẽ chứa độ lệch mới. Quá trình này được minh họa trên Hình 46.

1* Tất cả các bit trong byte có giá trị là 1

Y 1001 SS11 (các bit S là không xác định)

Hình 46 - Hoạt động hiệu chỉnh con trỏ AU-4 - chèn âm

Trong khung AU-3, byte chèn âm xuất hiện trong byte H3 của khung AU-3 có chứa các bit D bị đảo. Con trỏ tiếp theo sẽ chứa độ lệch mới. (xem minh họa trên Hình 47)

Hình 47 - Hoạt động hiệu chỉnh con trỏ AU-3 - Chèn âm

7.1.4 Cờ dữ liệu mới (NDF)

Bit 1-4 (N-bit) của từ con trỏ chứa NDF cho phép sự thay đổi tùy ý của con trỏ nếu nguyên nhân của sự thay đổi này là do sự thay đổi trong phần tải tin. Chế độ hoạt động bình thường được chỉ thị bởi mã "0110" trong các N-bit. NDF được chỉ thị bằng việc đảo các N-bit thành "1001". NDF được hiểu là cho phép khi có 3 hoặc nhiều hơn 3 bit trong 4 bit trùng với mẫu "1001". NDF được hiểu là bị vô hiệu hóa khi có 3 hoặc nhiều hơn 3 bit trong 4 bit trùng với mẫu "0110". Các giá trị còn lại ("0000", "0011", "0101", "1010", "1100" và "1111") được hiểu là các giá trị không hợp lệ.

7.1.5 Tạo con trỏ

Các qui tắc để tạo con trỏ AU-n:

1. Ở trạng thái hoạt động bình thường, con trỏ chỉ ra vị trí bắt đầu của VC-n trong khung AU-n. NDF được thiết lập về "0110"

2. Giá trị con trỏ có thể thay đổi bởi một trong các hoạt động ở các bước 3, 4, 5

3. Nếu có yêu cầu chèn dương, giá trị của con trỏ hiện tại được gửi với các bit I được đảo ngược và cơ hội chèn dương tiếp theo đó được điền đầy với thông tin giả. Các con trỏ tiếp theo chứa giá trị bằng giá trị của con trỏ trước được tăng thêm 1 đơn vị. Nếu giá trị của con trỏ đã đạt cực đại, con trỏ tiếp theo sẽ được thiếp lập về 0. Không có hoạt động tăng hay giảm con trỏ xảy ra trong tối thiểu 3 khung liên tiếp.

4. Nếu có yêu cầu chèn âm, giá trị của con trỏ hiện tại được gửi với các bit D được đảo ngược và cơ hội chèn âm tiếp theo đó được điền đầy với thông tin thật. Các con trỏ tiếp theo chứa giá trị bằng giá trị của con trỏ trước được giảm đi 1 đơn vị. Nếu giá trị của con trỏ đã đạt 0, con trỏ tiếp theo sẽ được thiết lập về giá trị cực đại. Không có hoạt động tăng hay giảm con trỏ xảy ra trong tối thiểu 3 khung liên tiếp.

5. Nếu có sự thay đổi trong việc ánh xạ VC-n vì các lý do nào khác với điểm 3 và 4 ở trên, giá trị con trỏ mới phải được gửi đi kèm theo NDF được thiết lập về "1001". NDF chỉ xuất hiện trong khung đầu tiên (là khung có chứa các giá trị mới). Vị trí mới của VC-n sẽ bắt đầu tại độ lệch được thiết lập bởi giá trị mới của con trỏ. Không có hoạt động tăng hay giảm con trỏ xảy ra trong tối thiểu 3 khung liên tiếp.

7.1.6 Thông dịch con trỏ

Các qui tắc thông dịch con trỏ:

1. Ở chế độ làm việc bình thường, con trỏ xác định vị trí bắt đầu của VC-n trong khung AU-n.

2. Bất kỳ sự thay đổi nào về giá trị của con trỏ hiện tại cũng đều được bỏ qua trừ khi có giá trị thích hợp mới của con trỏ xuất hiện trong 3 khung liên tiếp hoặc trước đó có xảy ra một trong ba các hoạt động 3, 4 hoặc 5 ở trên.

3. Nếu đa số trong số các bit I bị đảo, tức là chỉ thị có chèn dương. Giá trị con trỏ tiếp theo đó sẽ được tăng lên 1 đơn vị.

4. Nếu đa số trong số các bit D bị đảo, tức là chỉ thị có chèn âm. Giá trị con trỏ tiếp theo đó sẽ bị giảm đi 1 đơn vị.

5. Nếu giá trị của cờ NDF là cho phép, thì giá trị con trỏ coincident sẽ thay thế giá trị con trỏ hiện tại với độ lệnh được chỉ thị bởi con trỏ mới trừ trường hợp bộ thu ở trạng thái mắt con trỏ.

7.1.7 Liên kết các AU-4

Xem 10.1 và 10.2.

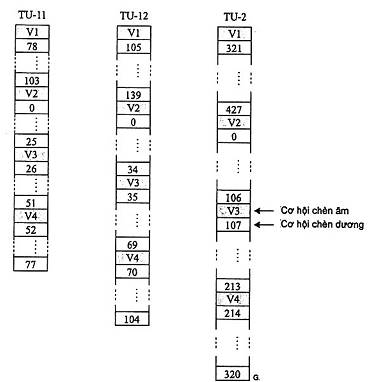

7.2 Con trỏ TU-3

7.2.1 Vị trí của con trỏ TU-3

Ba con trỏ TU-3 được chứa riêng biệt trong 3 byte H1, H2 và H3 như trên Hình 48.

Hình 48 - Đánh số độ bù con trỏ TU-3

7.2.2 Giá trị con trỏ TU-3

Giá trị con trỏ chứa trong các byte H1 và H2 chỉ ra vị trí bắt đầu của VC-3. Hai byte dành cho chức năng con trỏ được ghép thành một từ như trên Hình 43. Mười bit cuối cùng của từ con trỏ (bit 7 - 16) mang giá trị con trỏ.

Giá trị của con trỏ TU-3 là một số nhị phân nằm trong phạm vi từ 0-764, giá trị này chỉ ra độ lệch giữa con trỏ và byte đầu tiên của VC-3 (xem Hình 48).

7.2.3 Hiệu chỉnh tần số

Khi có sự lệch về tần số giữa tốc độ khung của TU-3 và VC-3, giá trị con trỏ sẽ tăng lên hoặc giảm đi tùy theo đó là chèn dương hay chèn âm. Hoạt động của con trỏ phải được phân cách nhau tối thiểu là 3 khung (tức là theo các nhóm 4 khung) trong đó khoảng thời gian đó giá trị của con trỏ được giữ nguyên.

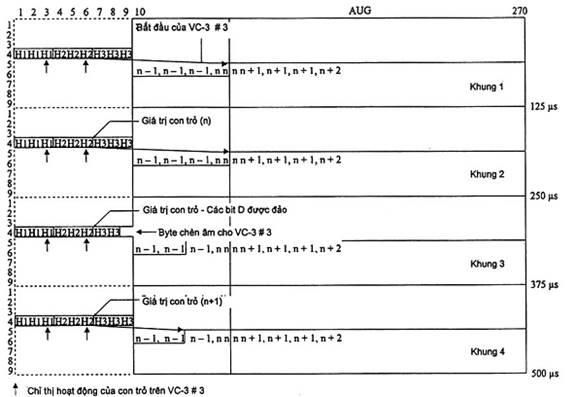

Nếu tốc độ khung của VC-3 quá chậm so với TU-3, giá trị của con trỏ sẽ tăng lên 1 đơn vị. Hoạt động này được chỉ thị bằng việc đảo các bit 7, 9, 11, 13 và 15 (I- bit) trong từ con trỏ để cho phép lựa chọn theo đa số của 5 bit tại bộ thu. Byte chèn dương xuất hiện ngay sau từng byte H3 trong khung TU-3 chứa các bit I đã được đảo. Các con trỏ TU-3 tiếp theo sẽ chứa độ lệch mới.

Nếu tốc độ khung của VC-3 quá nhanh so với TU-3, giá trị của con trỏ sẽ giảm đi 1 đơn vị. Hoạt động này được chỉ thị bằng việc đảo các bit 8, 10, 12, 14 và 16 (D- bit) trong từ con trỏ để cho phép lựa chọn theo đa số của 5 bit tại bộ thu. Các byte chèn âm xuất hiện ngay trong từng byte H3 trong khung TU-3 chứa các bit D đã được đảo. Các con trỏ TU-3 tiếp theo sẽ chứa độ lệch mới.

7.2.4 Cờ dữ liệu mới (NDF)

Bit 1-4 (N-bit) của từ con trỏ chứa NDF cho phép sự thay đổi tùy ý của con trỏ nếu nguyên nhân của sự thay đổi này là do sự thay đổi trong VC-3. Chế độ hoạt động bình thường được chỉ thị bởi mã "0110" trong các N-bit. NDF được chỉ thị bằng việc đảo các N-bit thành "1001". NDF được hiểu là cho phép khi có 3 hoặc nhiều hơn 3 bit trong 4 bit trùng với mẫu "1001". NDF được hiểu là bị vô hiệu hóa khi có 3 hoặc nhiều hơn 3 bit trong 4 bit trùng với mẫu "0110". Các giá trị còn lại ("0000", "0011", "0101", "1010", "1100" và "1111") được hiểu là các giá trị không hợp lệ. Việc đồng bộ mới được chỉ thị bằng giá trị của con trỏ kèm theo đó là NDF có tác dụng tại độ lệch được chỉ thị.

7.2.5 Tạo con trỏ

1. Ở trạng thái hoạt động bình thường, con trỏ chỉ ra vị trí bắt đầu của VC-3 trong khung TU-3. NDF được thiết lập về "0110"

2. Giá trị con trỏ có thể thay đổi bởi một trong các hoạt động ở các bước 3, 4, 5.

3. Nếu có yêu cầu chèn dương, giá trị của con trỏ hiện tại được gửi với các bit I được đảo ngược và cơ hội chèn dương tiếp theo đó được điền đầy với thông tin giả. Các con trỏ tiếp theo chứa giá trị bằng giá trị của con trỏ trước được tăng thêm 1 đơn vị. Nếu giá trị của con trỏ đã đạt cực đại, con trỏ tiếp theo sẽ được thiết lập về 0. Không có hoạt động tăng hay giảm con trỏ xảy ra trong tối thiểu 3 khung liên tiếp.

4. Nếu có yêu cầu chèn âm, giá trị của con trỏ hiện tại được gửi với các bit D được đảo ngược và cơ hội chèn âm tiếp theo đó được điền đầy với thông tin thật. Các con trỏ tiếp theo chứa giá trị bằng giá trị của con trỏ trước được giảm đi 1 đơn vị. Nếu giá trị của con trỏ đã đạt 0, con trỏ tiếp theo sẽ được thiết lập về giá trị cực đại. Không có hoạt động tăng hay giảm con trỏ xảy ra trong tối thiểu 3 khung liên tiếp.

5. Nếu có sự thay đổi trong việc ánh xạ VC-3 vì các lý do nào khác với điểm 3 và 4 ở trên, giá trị con trỏ mới phải được gửi đi kèm theo NDF được thiết lập về "1001". NDF chỉ xuất hiện trong khung đầu tiên (là khung có chứa các giá trị mới). Vị trí mới của VC-3 sẽ bắt đầu tại độ lệch được thiết lập bởi giá trị mới của con trỏ. Không có hoạt động tăng hay giảm con trỏ xảy ra trong tối thiểu 3 khung liên tiếp.

7.2.6 Thông dịch con trỏ

Các qui tắc thông dịch con trỏ:

1. Ở chế độ làm việc bình thường, con trỏ xác định vị trí bắt đầu của VC-3 trong khung TU-3

2. Bất kỳ sự thay đổi nào về giá trị của con trỏ hiện tại cũng đều được bỏ qua trừ khi có giá trị thích hợp mới của con trỏ xuất hiện liên trong 3 khung liên tiếp hoặc trước đó có xảy ra một trong ba các hoạt động 3, 4 hoặc 5 ở trên (xem 8.2.5)

3. Nếu đa số trong số các bit I bị đảo, tức là chỉ thị có chèn dương, giá trị con trỏ tiếp theo đó sẽ được tăng lên 1 đơn vị.

4. Nếu đa số trong số các bit D bị đảo, tức là chỉ thị có chèn âm, giá trị con trỏ tiếp theo đó sẽ bị giảm đi 1 đơn vị

5. Nếu giá trị của cờ NDF là cho phép, thì giá trị con trỏ mới sẽ thay thế giá trị con trỏ hiện tại với độ lệch được chỉ thị bởi con trỏ mới trừ trường hợp bộ thu ở trạng thái mất con trỏ. Con trỏ TU-2, TU-12 và TU-11.

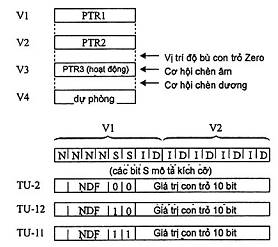

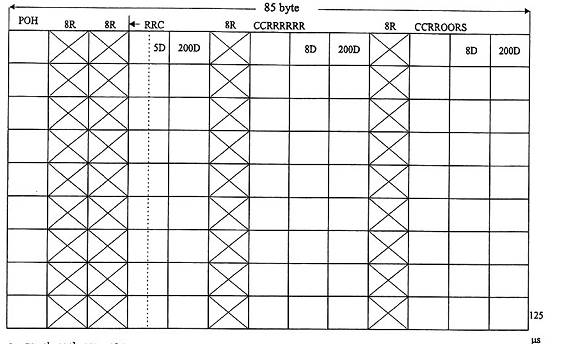

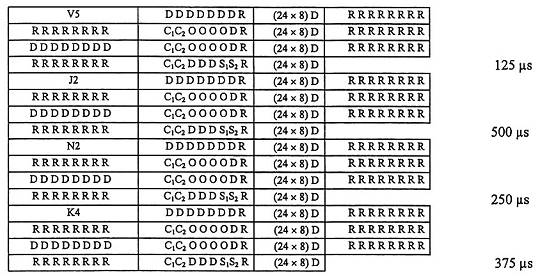

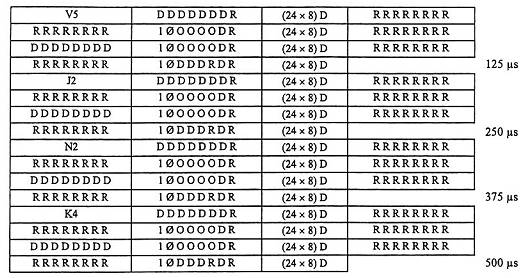

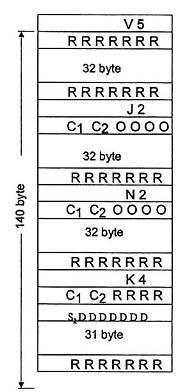

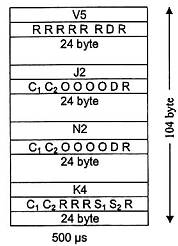

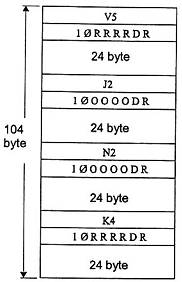

7.3 Con trỏ TU-2, TU-12 và TU-11

7.3.1 Vị trí của con trỏ TU-2, TU-12 và TU-11

Các con trỏ TU-2, TU-12 và TU-11 được chứa trong các byte V1 và V2 như quy định trên Hình 49.

TU Khối nhánh

VC Con-ten-nơ ảo

V1 Con trỏ TU thứ nhất

V2 Con trủ TU thứ 2

V3 Con trỏ TU thứ 3

V4 Dự phòng

CHÚ THÍCH - Các V1, V2, V3 và V4 là một phần của TU-n và được kết cuối tại bộ xử lý con trỏ

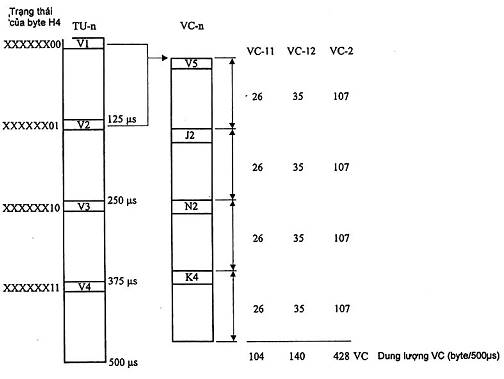

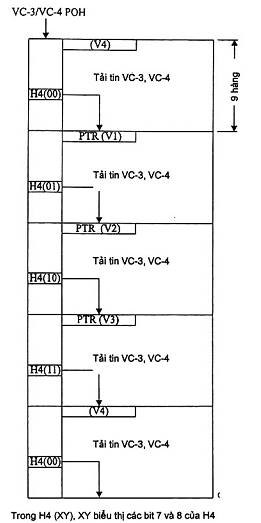

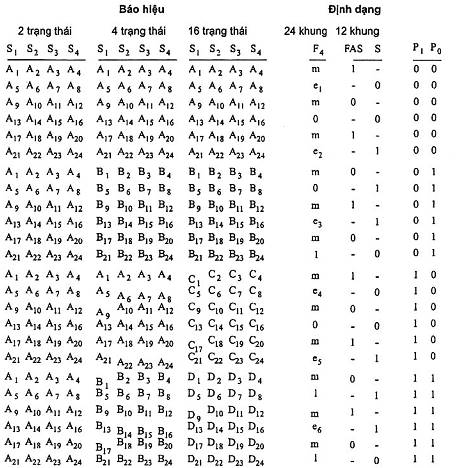

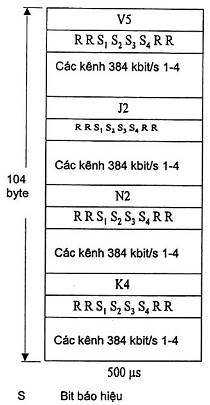

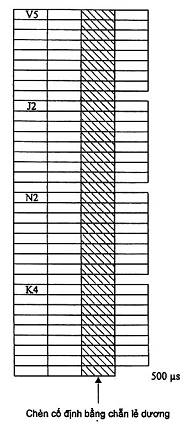

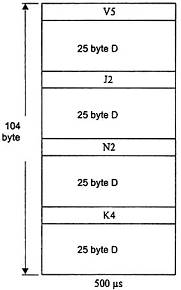

Hình 49 - Ánh xạ các container ảo trong đa khung TU

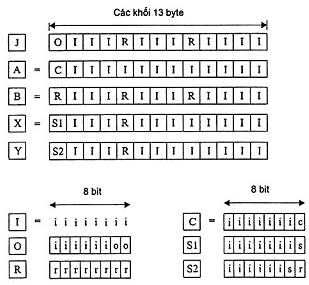

7.3.2 Giá trị của con trỏ TU-2, TU-12 và TU-11

Từ con trỏ TU được quy định trên Hình 50. Hai bit S (bit 5 và bit 6) chỉ ra loại TU. Giá trị con trỏ (nằm ở các bit 7 - 16) là một số nhị phân chỉ ra độ lệch giữa byte V2 và byte đầu tiên của VC-2, VC-12 hoặc VC-11. Phạm vi của độ lệch là khác nhau đối với từng loại TU như quy định trên Hình 51. Các byte con trỏ không được tính đến khi tính toán độ lệch.

I Tăng

D Giảm

N Cờ dữ liệu mới

Cờ dữ liệu mới

- Cho phép khi có tối thiểu 3 trong 4 bit trùng với mẫu "1001"

- Bị vô hiệu hóa khi có tối thiểu 3 trong 4 bit trùng với mẫu "0110"

- Không hợp lệ với các mã khác

Chèn âm

- Đảo 5 D-bit

- Chấp nhận các bit có ý nghĩa lớn nhất

| Giá trị con trỏ - Dải bình thường là: Đối với TU-2: 0-427 nhị phân Đối với TU-12: 0-139 nhị phân Đối với TU-11: 0-103 nhị phân | Chèn dương - Đảo 5 I-bit - Chấp nhận các bit có ý nghĩa lớn nhất Chỉ thị liên kết - 1001SS1111111111 (SS là các bit không được xác định) |

Hình 50 - Mã hóa con trỏ TU-2, TU-12 và TU-11

V1 PTR1

V2 PTR2

V3 PTR3 (hoạt động)

V4 Dự phòng

Hình 51 - Bù con trỏ TU-2, TU-12 và TU-11

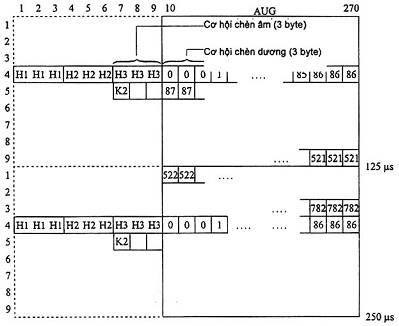

7.3.3 Hiệu chỉnh tần số của TU-2, TU-12 và TU-11

Con trỏ TU-2, TU-12 và TU-11 được sử dụng để hiệu chỉnh tần số của VC-2, VC-12, VC-11 theo cách giống như con trỏ TU-3 được sử dụng để hiệu chỉnh tần số của VC-3. Cơ hội chèn dương nằm ngay sau byte V3. Ngoài ra, V3 cũng được sử dụng như cơ hội chèn âm khi có chèn âm xảy ra, khi đó V3 sẽ được dùng cho tải tin. Điều này được minh họa trên Hình 51. Việc chỉ thị có hay không có cơ hội chèn được thực hiện bằng các bit I và D của con trỏ trong đa khung TU hiện tại. Giá trị chứa trong V3 khi không được sử dụng cho chèn âm không được quy định. Bộ thu sẽ bỏ qua giá trị chứa trong V3 bất cứ khi nào byte V3 không được sử dụng cho chèn âm.

7.3.4 Cờ dữ liệu mới (NDF)

Bit 1-4 (N-bit) của từ con trỏ chứa NDF cho phép sự thay đổi tùy ý của con trỏ nếu nguyên nhân của sự thay đổi này là do sự thay đổi trong phần tải tin. 4 bit được sử dụng cho NDF nhằm cho phép việc sửa lỗi. Chế độ hoạt động bình thường được chỉ thị bởi mã "0110" trong các N-bit. NDF được chỉ thị bằng việc đảo các N-bit thành "1001". NDF được hiểu là cho phép khi có 3 hoặc nhiều hơn 3 bit trong 4 bit trùng với mẫu "1001". NDF được hiểu là bị vô hiệu hóa khi có 3 hoặc nhiều hơn 3 bit trong 4 bit trùng với mẫu "0110". Các giá trị còn lại ("0000", "0011", "0101", "1100" và "1111") được hiểu là các giá trị không hợp lệ. Việc đồng bộ mới được chỉ thị bằng giá trị của con trỏ và kèm theo đó là NDF có tác dụng tại độ lệch được chỉ thị.

7.3.5 Tạo và thông dịch con trỏ TU-2, TU-12 và TU-11

Các quy định về tạo và thông dịch con trỏ TU-2, TU-12 và TU-11 cho VC-2, VC-12 và VC-11 tương tự các qui tắc được quy định ở 7.2.5 và 7.2.6 cho con trỏ TU-3 trong đó TU-3 được thay thế bằng TU-2, TU-12 hoặc TU-11 và VC-3 được thay thế bằng VC-2, VC-12 hoặc VC-11.

7.3.6 Liên kết TU-2

Xem quy định trong 10.3 và 10.4

7.3.7 Kích thước của TU-2, TU-12 và TU-11

Các bít 5 và 6 của con trỏ TU-2, TU-12 và TU-11 chỉ ra kích thước của TU-m. Có 3 loại kích thước như quy định trên Bảng 5 dưới đây:

Bảng 5 - Kích thước của TU-2, TU-12 và TU-11

| Kích thước | Loại tải | Phạm vi của con trỏ TU-m (trong 500 ms) |

| 00 | TU-2 | 0-427 |

| 10 | TU-12 | 0-139 |

| 11 | TU-11 | 0-103 |

| CHÚ THÍCH - Kỹ thuật này chỉ sử dụng cho các mức TU-2, TU-12 và TU-11 | ||

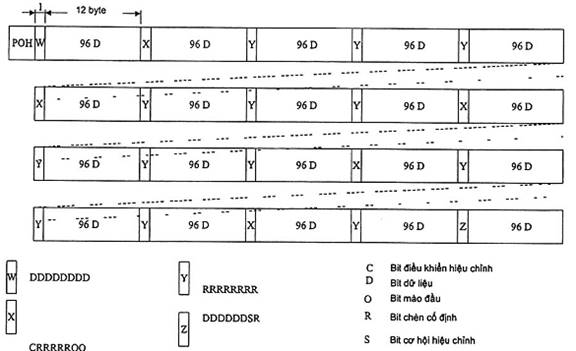

7.3.8 Byte chỉ thị đa khung TU-2, TU-12 VÀ TU-11

Byte chỉ thị đa khung TU-2, TU-12 và TU-11 (byte H4) liên quan đến mức thấp nhất của cấu trúc ghép kênh và cung cấp đa khung 500 ms (4-khung). Byte này xác định khung chứa con trỏ TU-2, TU-12 hoặc TU-11. Trên Hình 49 chỉ ra cách ánh xạ các VC-2, VC-12 và VC-11 vào trong đa khung TU-2, TU-12 và TU-11. Giá trị của byte H4, đọc từ VC-4/VC-3 POH chỉ ra pha khung của tải VC-4/VC-3 tiếp theo (xem Hình 52). Mã hóa của byte H4 được quy định trên Hình 53.

Hình 52 - Chỉ thị đa khung 500 ms TU-2, TU-12 và TU-11 sử dụng byte H4

Các bit trong byte H4

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | Khung số | Thời gian |

| X X X X | X X X X | 1 1 1 1 | 1 1 1 1 | X X X X | X X X X | 0 0 1 1 | 0 1 0 1 | 0 1 2 3 | 0

Đa khung TU-m 500 ms |

X Bit dành cho chuẩn hóa quốc tế trong tương lai. Trong nội địa, giá trị của bit này được đặt là "1".

Hình 53 - Quy định về chuỗi mã hóa byte H4 trong chỉ thị đa khung TU

8. Yêu cầu kỹ thuật cho các byte mào đầu

8.1 Các loại mào đầu

8.1.1 SOH

Thông tin SOH là thông tin được ghép thêm vào phần tải tin để tạo ra khung STM-N. SOH được quy định bao gồm các thông tin về đồng bộ khung, thông tin về bảo dưỡng, thông tin về giám sát chất lượng và các chức năng hoạt động khác. Thông tin SOH được chia thành thông tin mào đầu đoạn lặp (RSOH) và thông tin mào đầu đoạn ghép kênh (MSOH). RSOH được kết cuối tại các chức năng của trạm lặp, còn MSOH được truyền tải trong suốt quá trình lặp và được kết cuối tại các điểm mà AUG-N được tổng hợp nên hoặc tách thành các nhánh thành phần.

CHÚ THÍCH: Phần mào đầu FEC được định nghĩa trong 9.2.4 sử dụng cả RSOH và MSOH. Vì FEC được định nghĩa cho đoạn ghép kênh nên phần mào đầu FEC trong RSOH không được kết cuối tại các chức năng trạm lặp.

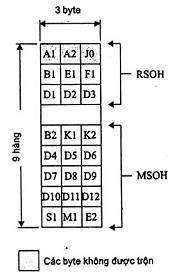

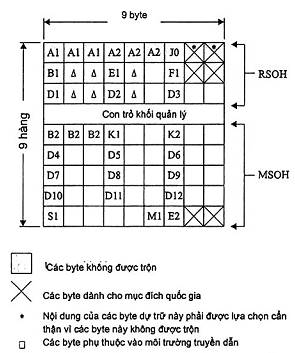

Các dòng từ 1-3 của SOH được dành cho RSOH, các dòng từ 5-9 được dành cho MSOH. Trên Hình 56 dưới đây là SOH của STM-1. Chi tiết về SOH được quy định trong 8.2

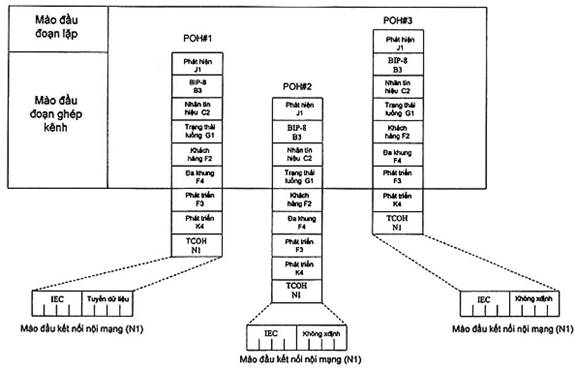

8.1.2 POH của Container ảo (VC-POH)

VC-POH được sử dụng để đảm bảo tính toàn vẹn về thông tin giữa hai điểm ghép vào tách ra của container ảo. Có hai loại VC-POH:

- VC-POH bậc cao (VC-4/VC-3 POH): VC-3 POH được ghép vào TUG-2 hoặc C-3 để tạo nên VC-3. VC-4 POH được ghép vào TUG-3 hoặc C-4 để tạo nên VC-4. Các chức năng của POH container ảo bậc cao bao gồm: giám sát chất lượng luồng container ảo, chỉ thị trạng thái cảnh báo, các tín hiệu dành cho mục đích bảo dưỡng và chỉ thị cấu trúc ghép kênh.

- VC-POH bậc thấp (VC-3/VC-2/VC-12/VC-11 POH): POH VC-m bậc thấp (m=11, 12, 2, 3) được ghép vào C-m để tạo nên VC-4. VC-4 POH được ghép vào TUG-3 hoặc C-4 để tạo nên VC-4.

Các chức năng của POH của container ảo bậc thấp bao gồm: giám sát chất lượng luồng container ảo, chỉ thị trạng thái cảnh báo, các tín hiệu dành cho mục đích bảo dưỡng.

Các yêu cầu chi tiết đối với POH được quy định trong 8.3.

8.2 Mô tả SOH

8.2.1 Vị trí của các byte SOH

Vị trí của các byte SOH trong khung STM-N, N ³ 1 được xác định bởi vector S 3 chiều: S(a, b, c), trong đó a(1-3, 5-9) là số của hàng, b(1-9) là số của đa cột và c(1-N) là độ sâu ghép trong đa cột. Xem minh họa trên Hình 54.

Mối quan hệ giữa số của cột và hàng và các tọa độ của vector như sau:

Hàng = a

Cột = N(b-1) + c

Đối với STM-0, việc xác định các byte SOH bằng vector 3 chiều là không cần thiết vì tất cả các byte SOH của STM-0 đều có tên <chữ cái> <số>.

Hình 54 - Đánh số vị trí của các byte SOH trong khung STM-N

Nội dung của các byte SOH trong khung STM-0/1/4/16/64/256 được quy định trong các hình từ Hình 55 đến Hình 60.

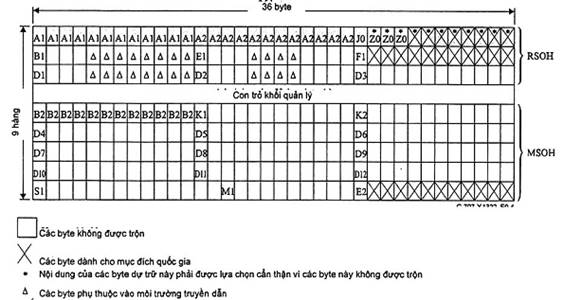

Hình 55 - STM-0 SOH

CHÚ THÍCH - Tất cả các byte không được đánh dấu là được để dành sử dụng cho chuẩn hóa quốc tế trong tương lai (phụ thuộc vào môi trường truyền dẫn, cho mục đích của quốc gia và cho các mục đích sử dụng khác)

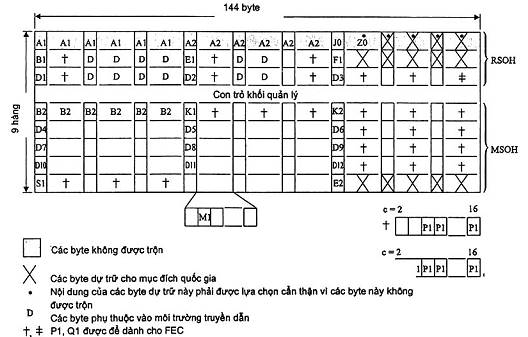

Hình 56 - STM-1 SOH

CHÚ THÍCH - Tất cả các byte không được đánh dấu là được để dành cho sử dụng cho chuẩn hóa quốc tế trong tương lai (phụ thuộc vào môi trường truyền dẫn, cho mục đích quốc gia và cho các mục đích sử dụng khác)

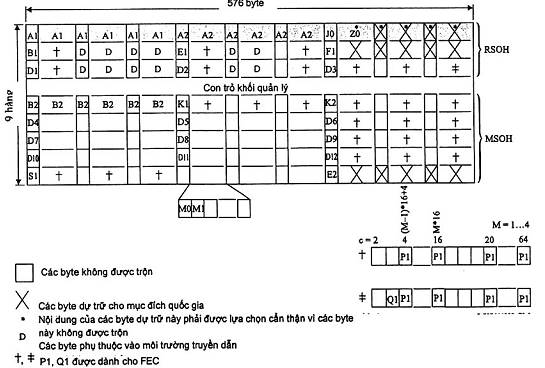

Hình 57 - STM-4 SOH

CHÚ THÍCH - Tất cả các byte không được đánh dấu là được để dành cho sử dụng cho chuẩn hóa quốc tế trong tương lai (phụ thuộc vào môi trường truyền dẫn, cho mục đích quốc gia và cho các mục đích sử dụng khác)

Hình 58 - STM-16 SOH

CHÚ THÍCH - Tất cả các byte không được đánh dấu là được để dành cho sử dụng cho chuẩn hóa quốc tế trong tương lai (phụ thuộc vào môi trường truyền dẫn, cho mục đích quốc gia và cho các mục đích sử dụng khác)

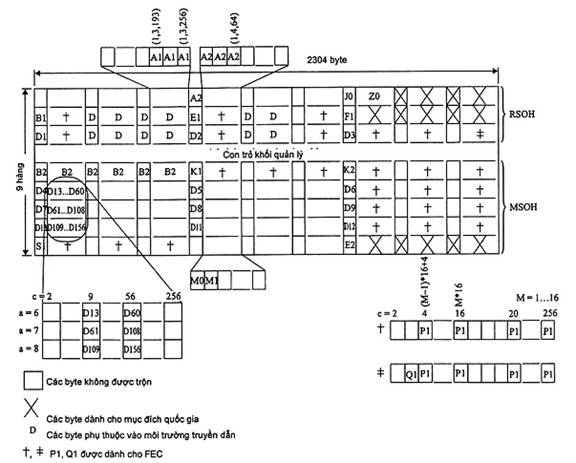

Hình 59 - STM-64 SOH

CHÚ THÍCH - Tất cả các byte không được đánh dấu là được để dành cho sử dụng cho chuẩn hóa quốc tế trong tương lai (phụ thuộc vào môi trường truyền dẫn, cho mục đích quốc gia và cho các mục đích sử dụng khác)

Hình 60 - STM-256 SOH

8.2.2 Mô tả các byte SOH

8.2.2.1 Đồng bộ khung: A1, A2

Có hai loại byte được định nghĩa cho đồng bộ khung:

- A1: 11110110

- A2: 00101000

Từ đồng bộ khung của khung STM-0 bao gồm một byte A1 và sau đó là một byte A2. Từ đồng bộ khung của khung STM-N (N=1, 4, 16, 64) bao gồm 3 x N byte A1 và sau đó là 3 x N byte A2. Từ đồng bộ khung của khung STM-256 bao gồm 64 byte A1 ở các vị trí từ S (1,3,193) [1,705] đến S (1,4,64) [1,832]. Các byte ở các vị trí S (1,1,1) [1,1] đến S (1,3,192) [1,704] và S (1,465) [833] đến S (1,9,256) [1,1536] được dành cho tương lai.

CHÚ THÍCH: Đối với các byte được dự trữ nằm trong hàng 1 của khung STM-256, lưu ý khi chọn mẫu để đảm bảo cung cấp đủ chuyển tiếp tín hiệu và không có sự mất cân bằng đáng kể nào về DC sau khi tín hiệu được trộn.

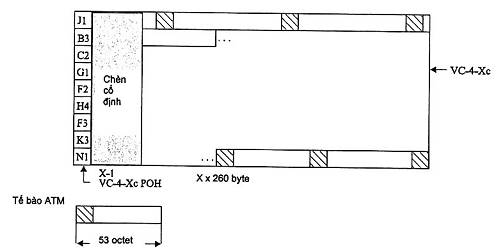

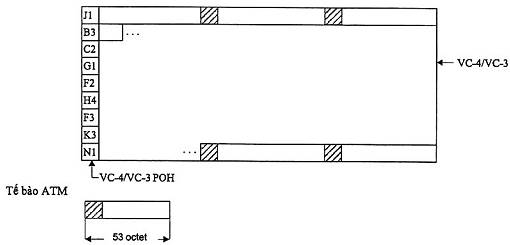

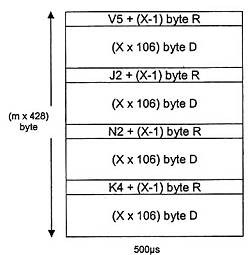

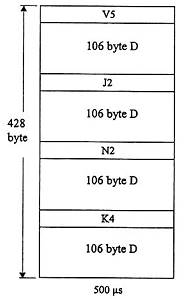

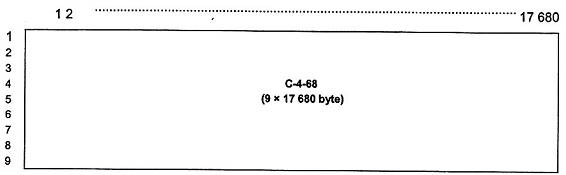

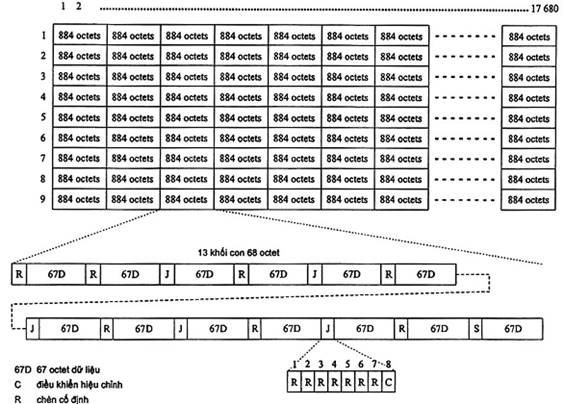

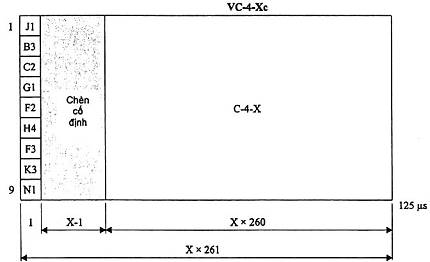

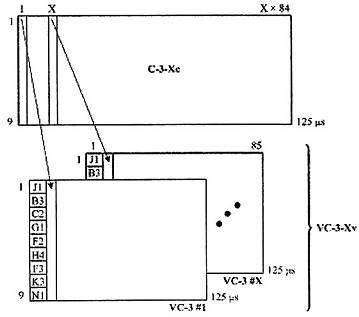

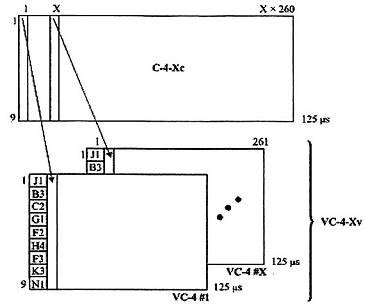

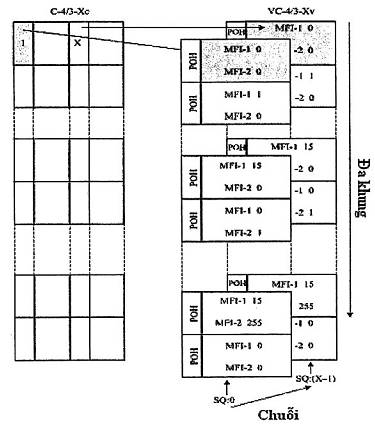

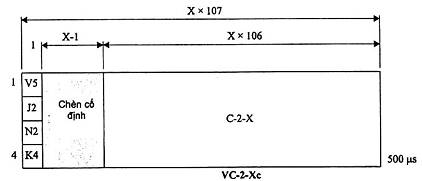

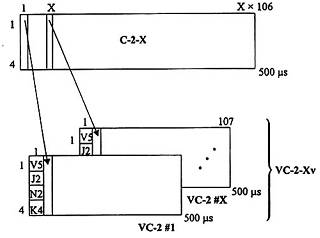

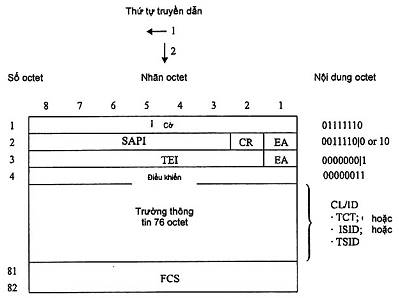

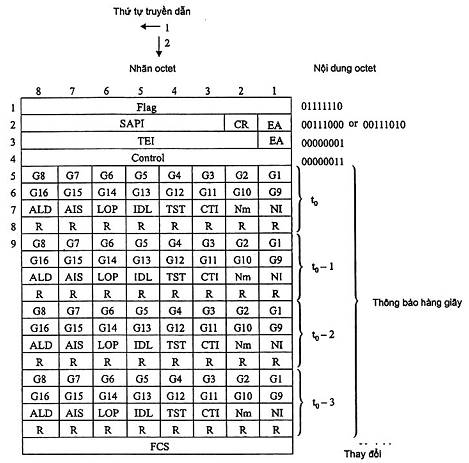

8.2.2.2 Truy vết đoạn trạm lặp: J0